· 193 ·

DOI: 10. 13382/j. jemi. B2407690

# 非线性超声短脉冲信号检测方法研究与实现\*

谢子成1 郑隆浩1 邹 涌1 唐立军1,2

(1.长沙理工大学物理与电子科学学院 长沙 410114;

2. 近地空间电磁环境检测与建模湖南省高校重点实验室 长沙 410114)

摘 要:一般的微弱信号检测方法所使用的锁相放大技术对于高频短脉冲信号还存在困难。对于一般的锁相放大器而言,短脉冲信号达不到锁相放大器后级滤波器的建立时间,难以检测到微弱的高频短脉冲信号,因此提出了一种针对高频非线性超声短脉冲信号的检测方法。该方法在锁相放大技术的基础上,考虑到非线性超声信号为周期信号,在锁相放大器的前级增加数字平均环节,增大信号的信噪比。锁相放大环节中采用滑动均值滤波代替普通低通滤波器,根据最佳匹配原则,设置滑动均值滤波器的窗长度等于脉冲持续时间,实现只对脉冲信号进行的低通滤波,避免了普通低通滤波器对短脉冲信号建立时间不够的问题,最终实现高频非线性短脉冲信号检测的锁相放大。本系统采用数模混合电路,逻辑算法部署在 FPGA 上。采用微弱信号发射器与电脑端搭建测试平台,对系统进行测试。测试结果表明,在输入信号频率为分别为 0.6 、1、2、5、10 MHz 的情况下,系统均能检测到脉冲长度为 5 µS,幅度为 100 nV 的脉冲信号,并且具有良好的线性度。选择频率为 1 MHz 的输入信号进行不同脉冲宽度的测试,系统能准确检测到脉冲长度为 5、10、30 µS,幅度大小为 100 nV 的脉冲信号。

关键词:锁相放大器;滤波器;数字平均;短脉冲信号检测

中图分类号: TN98 文献标识码: A 国家标准学科分类代码: 510.1010;510.4010

# Research and implementation of nonlinear ultrasonic short pulse signal detection method

Xie Zicheng<sup>1</sup> Zheng Longhao<sup>1</sup> Zou Yong<sup>1</sup> Tang Lijun<sup>1,2</sup>

School of Physics and Electronic Science, Changsha University of Science and Technology, Changsha 410114, China;

Key Laboratory of Electromagentic Environment Detection and Modeling in Near-Earth Space of Hunan Province Universities, Changsha 410114, China)

Abstract: The phase-locked amplification technique used in the general weak signal detection method is still difficult for high frequency short pulse signal. For the general phase-locked amplifier, the short pulse signal cannot reach the establishment time of the post-stage filter of the phase-locked amplifier, so it's difficult to detect the weak high-frequency short pulse signal. Considering that the nonlinear ultrasonic signal is periodic signal, add digital average to the front stage of the phase-locked amplifier to increase the signal-to-noise ratio of the signal. According to the principle of best matching, the window length of the moving mean filter is set equal to the pulse duration, so as to realize the low-pass filtering only for the pulse signal, avoiding the problem that the common low-pass filter does not have enough time to establish the short pulse signal, and finally realizing the phase-lock amplification of high-frequency nonlinear short pulse signal detection. The system uses mixed digital analog circuit, and the logic algorithm deployed on the FPGA. The weak signal transmitter and computer are used to build a test platform to test the system. The test results show that the system can detect the pulse signals with a pulse length of 5  $\mu$ S and amplitude of 100 nV when the input signal frequencies are respectively 0.6, 1, 2, 5 and 10 MHz, and has good linearity. Select the signal with frequency of 1 MHz for different pulse width test, the system can accurately detect pulse signals with pulse length of 5, 10, 30  $\mu$ S and amplitude of 100 nV.

**Keywords**: phase-locked amplifier; filter; digital averaging; short pulse signal detection

# 0 引 言

在非线性超声无损检测中,非线性超声激励信号经过被检测物体后,如果物体有损伤,会在损伤处发生非线性效应。可通过分析非线性效应形成的透射波信号的幅值了解到物体内部的一些信息<sup>[1-3]</sup>。对于硬质合金或者较厚的物体,非线性超声的激励信号功率可达到 kW 级,且频率很高,很难做到连续发射,所以目前在无损检测中都是采用脉冲发射。激励信号在物体内部传播时,会产生很大的衰减,并且会叠加各种噪声,如环境中的电磁噪声,热噪声,器件的噪声等,这些噪声以各种方式叠加在透射波信号上,使得对分析有用的透射脉冲信号完全淹没在噪声中。

对于淹没在噪声中的信号,比较常用的检测方式为 锁相放大技术[4]。采用传统的锁相放大器结构,对于连 续信号,检测精度可以达到 1 nV。锁相放大器的性能和 滤波器的带宽有直接关系,滤波器的带宽越窄,锁相放大 器的性能就越好[5]。对于脉冲信号,如果滤波器的带宽 越窄,对于信号的建立时间就会越长,如果滤波器的建立 时间大于脉冲信号的持续时间,脉冲信号则会衰减,难以 检测到脉冲信号。国外的学者 De 等[6-7] 采用纯模拟电路 搭建的锁相放大电路进行光脉冲信号的检测,分辨率只 有 25 μV。国内学者对于锁相放大器的研究也都专注在 检测连续信号,例如文献[8-9]利用锁相放大器来测量连 续性的光谱信号,文献[10-12]利用锁相放大器检测持续 存在的气体信号等,并没有学者提出用于微弱短脉冲信 号的锁相放大器方案。因此,研究一种用于微弱短脉冲 信号的锁相放大器方案是很有必要的。本研究针对微弱 短脉冲信号检测中滤波器建立时间与滤波器带宽相互矛 盾的问题,提出了一种将数字平均算法与滑动均值滤波 器用在锁相放大器结构中的微弱短脉冲信号检测方案, 避免了滤波器的带宽与建立时间相互矛盾的问题。

# 1 非线性超声短脉冲微弱信号检测方案

#### 1.1 锁相放大器原理

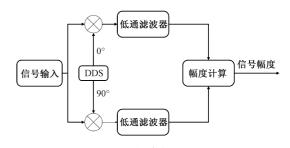

一般的锁相放大器原理如图 1 所示。

对于输入信号:  $S(t) = U(t)A\sin(wt + \alpha) + n(t)$ ,使用 DDS 生成两路与输入信号频率相同,并且相互正交的 参考信号[13-15]。

$$S_{\sin}(t) = B \sin wt \tag{1}$$

$$S_{\text{esc}}(t) = B\sin(wt + 90^\circ) \tag{2}$$

将输出信号与两路参考信号相乘,进行相敏检波,结果为:

图 1 锁相放大器原理

Fig. 1 Principle of phase-locked amplifier

$$S_{\text{psd\_sin}}(t) = U(t) \times \frac{AB}{2} \cos\alpha - U(t) \times \frac{AB}{2} \cos(2wt + \alpha) + n(t) \times B \sin wt$$

(3)

$$S_{\text{psd\_cos}}(t) = U(t) \times \frac{AB}{2} \cos(\alpha - 90^{\circ}) - U(t) \times C$$

$$\frac{AB}{2}\cos(2wt + \alpha + 90^\circ) + n(t)B\sin(wt + 90^\circ) \tag{4}$$

由式(3)与(4)可以看出,最后结果由 3 部分构成: 直流分量,二倍频分量和噪声分量。因为参考的正弦信 号为周期信号,而噪声为随机信号,噪声和信号不具有相 关性[16].因此这部分结果为 0。

对于一般的连续信号,一般使用低通滤波器进行低通滤波,滤除频率为 2 w 的频率分量后,通过式(5)即可算出待检测信号的幅度  $A^{[16-17]}$ 。

$$A = \frac{2 \times \sqrt{S_{\text{psd\_sin}}^2 + S_{\text{psd\_cos}}^2}}{B} \tag{5}$$

对于连续信号和理想的滤波器,在经过滤波器的建立时间,信号达到稳态之后,系统只剩下基频分量,通过式(5)即可算出信号的幅度。在实际情况中,要使实际滤波器的效果接近理想滤波器,需要滤波器的过渡带十分陡峭,就需要增加滤波器阶数,但是对于高阶的滤波器,其进入稳态的时间也会越来越长,对于短脉冲信号,如果滤波器进入稳态的时间大于了短脉冲信号的持续时间,则被测信号将会被滤除。

#### 1.2 微弱短脉冲锁相放大检测方案

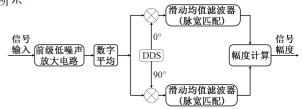

经过以上分析,将传统的锁相放大器改进如图 2 所示\_\_\_\_\_\_

图 2 微弱短脉冲锁相放大检测方案

Fig. 2 Weak short pulse phase lock amplification detection scheme

在非线性超声无损检测时,激励一般为脉冲的形式。 当对物体施加非线性超声激励信号时,非线性超声信号 经过有缺陷的物体,发生非线性效应形成透射波,往往表现为幅度上的变化,而脉冲的重复周期和脉冲宽度不会 因为透过物体发生改变。在后续研究中,设透射波信号 约束如式(6)所示。

$$\begin{cases} S(t) = U(t)A\sin(wt + \alpha) + n(t) \\ U(t) = u(t) - u(t - W) \\ \alpha = 0(t = t_d) \\ t_d + W \le T \end{cases}$$

(6)

其中, A 为待检测信号的幅值, w 为待检测信号的角频率,  $\alpha$  为输入信号的初始相位, n(t) 为信号在传输过程中因为各种原因所产生的加性噪声, u(t) 为阶跃函数,  $t_d$  为在一个重复周期内脉冲信号出现的时间延时, w 为脉冲信号的宽度, T 为脉冲信号重复的周期。在实际检测中, 噪声 n(t) 的幅值往往比待检测信号的幅值大许多倍, 导致信号被完全淹没在噪声中。

#### 1.3 前级低噪声放大电路分析

对于锁相放大系统而言,系统的最小分辨率直接取决于模数转换器(analog to digital converter, ADC)所能采集到的最小信号。而一般的高速 ADC 很难做到高精度,例如对于一个输入范围为 0~3.3 V 的 16 位 ADC 来说,其最小分辨率为:

$$LSB = \frac{3.3 \text{ V}}{2^{16} - 1} \approx 5 \times 10^{-5} \text{ V}$$

(7)

即对于小于 5  $\mu$ V 的信号, ADC 就无法采集到, 也无法通过算法分辨出来。

前级低噪声放大器的作用主要为在放大信号的同时,能够通过滤波器有效的抑制一部分高频噪声,一定程度上增大信号的信噪比。对于滤波器通带内的信号和噪声放大作用相同。假设原信号为 $S_{\iota}(t)$  =  $A\sin(wt + \alpha)$  +  $A_{\iota}n(t)$  ,其中A<5  $\mu$ V,即 ADC 的最小分辨率, $A_{\iota}$  为通带内噪声的平均幅度。级联放大器的放大倍数为M,放大后的信号为 $S_{M\iota}(t)$  =  $MA\sin(wt + \alpha)$  +  $MA_{\iota}n(t)$  。对于通带内的噪声而言,平均幅度被放大了M倍,对于被淹没在噪声中的信号,噪声的平均幅度远远的大于待检测信号的幅度,放大后的有效信号依然被淹没在噪声中。对于信号而言,当信号幅度MA>5  $\mu$ V 时,信号就大于了ADC的最小分辨率,能够被检测到,并且通过算法检测出来,即使它被淹没在噪声中。

#### 1.4 数字平均算法分析

对于被淹没在噪声中的透射波信号而言,其信噪比(signal to noise ratio, SNR)非常低。对于数字系统而言,当信噪比过低时,系统的计算压力会非常大,且效果不是很好,所以要尽可能的增大输入信号的信噪比,即系

统的信噪改善比(signal to noise improvement ratio, SNIR) 要足够大,才能保证检测的准确性。

数字平均算法常用在检测周期性信号的场合。假设 待检测信号  $S_i(t) = A(t) + n(t)$ ,其中 A(t) 为有用信号, n(t) 为噪声。由式(8) 可知,信号的重复周期为 T,设系 统所使用 ADC 的采样率为 fs,则信号的每个重复周期所 需要采样的点数 N 为:

$$N = T \times fs \tag{8}$$

则对于重复信号一个周期内的第 i(0 < i < N) 个点来说,进行i次数字平均操作的结果为:

$$S_{ii}(t) = \frac{1}{j} \sum_{j=0}^{N-1} A_i(t) + \frac{1}{j} \sum_{j=0}^{N-1} n_i(t)$$

(9)

由于当 $j \to + \infty$  时,对周期内某一个点的数字平均的结果为其数学期望值,所以由上式可得:

$$E[S_{i}(t)] = E[A_{i}(t)] + E[n_{i}(t)]$$

$$(10)$$

对于确定的信号 A(t),一个重复周期内第 i 个点的数学希望  $E[A_i(t)]$  为其信号本身。但对于普通的噪声 n(t),其在数学上的数学期望值为 0。所以当数字平均的次数足够多时,数字平均器输出信号的信噪比  $SNR=\frac{E[A(t)]}{0}=\infty$ ,所能达到的信噪改善比 SNIR 也为无穷大。

#### 1.5 低通滤波器与脉宽匹配

由式(1)~(5)可知,对于短脉冲信号,为了保证系统对二次谐波分量与噪声的有效滤除,需要滤波器的阶数足够高,而过高的阶数意味着滤波器进入稳态的时间更长,二者之间难以权衡。本研究使用滑动均值滤波器解决这一问题。

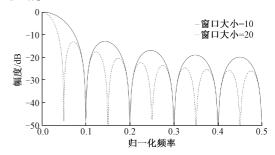

滑动均值滤波器本质上是一个低通滤波器,其输出结果是输入信号在一段时间内所有值的平均值。其幅频特性曲线如图 3 所示,分别是窗为 10 和窗为 20 时的滑动均值滤波器的幅频特性曲线,可以看出均有明显的低通特性,且随着窗的加大,滑动均值滤波器的过渡带变得愈发陡峭。

图 3 滑动均值滤波器频率响应

Fig. 3 Moving mean filter frequency response

在信噪比较高的情况下, 当滑动均值滤波器的窗的

大小与式(6)中的脉冲宽度 W 匹配或者小于脉冲宽度 时,滑动均值滤波器的输出将出现极值<sup>[18-19]</sup>,同时完成低通滤波器的作用,再通过式(5)即可算出待测脉冲信号的幅度。

系统如图 4 所示。系统以现场可编程逻辑阵列(field programmable gate array, FPGA)为主要计算控制单元,设计前级低噪声放大电路、ADC 转换电路和数字锁相放大,低噪声线性电源等。

## 2 系统电路与算法实现

根据非线性超声短脉冲微弱信号检测方案,设计了

图 4 系统实现框图 Fig. 4 System implementation block diagram

#### 2.1 前级低噪声放大电路

根据弗里斯公式,M级级联放大器的总噪声系数 F与增益 K的关系为:

$$F = F_1 + \frac{F_2 - 1}{K_1} + \frac{F_3 - 1}{K_1 K_2} + \cdots + \frac{F_M - 1}{K_1 K_2 \cdots K_{M-1}}$$

(11)

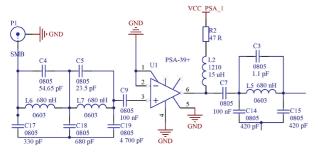

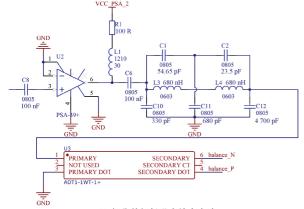

式(11)说明在级联放大系统中,对噪声贡献最大的为第一级放大器的噪声,所以在放大器的选择上,第一级放大器的选择尤为重要。因为本系统所需要采集的信号频率较高,且由式(7)可知,如需要采集到最小100 nV的电压,系统所需的放大倍数应大于500倍,如果使用集成运算放大器需要运放具有很大的增益带宽积,且对于高速信号,集成运放的寄生参数与系统噪声等都会对增大系统的噪声输入<sup>[20]</sup>,从而降低系统的信噪比。射频晶体管相较于集成运放,其结构简单,内部寄生参数较小,适用于高频且低噪声的场合。前级低噪声放大电路的电路图如图 5 所示。

前级 PSA-39+为固定增益射频放大器,该芯片内部结构及其简单,拥有极低的输入噪声和极高的带宽: DC-6 MHz 其在 100 kHz~10 MHz 的增益约为 20 dB。因为其输入阻抗为 50 Ω,所以前级无需进行阻抗匹配设计,为

了使前级达到更高的增益,故采用两级 PSA-39+串联,串联增益约为 40 dB。

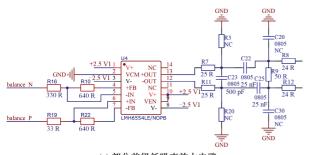

单端信号在传输过程中可能会受到环境中的各种干扰,影响信号质量。为了减小信号在传输过程中收到的各种干扰对后级检测的影响,中间级以及后级放大器采用差分传输的方式,最大程度的减小外界对系统的干扰。

射频放大后使用 ADT1-1WT+将单端信号转为差分信号。ADT1-1WT+为1:1 的平衡巴伦。巴伦为无源器件,相较于其他有源器件如单端转差分的集成运放来说,拥有更低的噪声,并且在 DC-10 MHz 时的插入损耗小于0.5 dB,满足设计需求。

差分传输端第一级使用超线性低噪声差分放大器 LMH6554,其输入电压噪声仅有 0.9 nV/√Hz,输入电流 噪声仅有 11 pA/√Hz。小信号带宽达 1.8 GHz 非常适用于高频信号处理,并且其压摆率达 6 200 nV/μS,能够迅速回应信号的变化。由式(7)可知,如需要采集到最小 100 nV 的电压,系统所需的放大倍数应大于 500 倍,即 53 dB 即可。使用两级 PSA-39+,每一级增益为 20 dB,所以还需要至少 13 dB 即 5 倍的放大倍数。在 1 MHz 的频率下需要的增益带宽积为:

$GBW = G \times f = 100 \times 1\ 000\ 000 = 100\ MHz$  (12) 所以该芯片完全满足设计需求。

(a) 部分前级低噪声放大电路 (a) Partial front low noise amplifier circuit

(b) 部分前级低噪声放大电路 (b) Partial front low noise amplifier circuit

(c) 部分前级低噪声放大电路 (c) Partial front low noise amplifier circuit

(d) 部分前级低噪声放大电路 (d) Partial front low noise amplifier circuit

图 5 前级低噪声放大电路

Fig. 5 Front low noise amplifier circuit

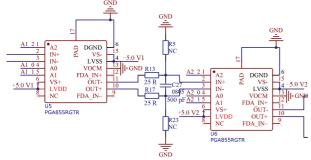

为了增加系统测量的动态范围,避免在测量大信号的时候出现失真的情况最后级联放大器的最后采用两片PGA855级联。PGA855是一款可编程增益的差分放大器,可以通过可知其引脚的高低电平控制芯片的增益,其增益控制如表1所示。

表 1 PGA855 增益控制 Table 1 PGA855 gain control

| A2:A0 | 000    | 001   | 010 | 011 | 100 | 101 | 110 | 111 |

|-------|--------|-------|-----|-----|-----|-----|-----|-----|

| 增益    | 0. 125 | 0. 25 | 0.5 | 1   | 2   | 4   | 8   | 16  |

PGA855 在全部增益控制模式下都能达到 10 MHz 的带宽,并且输入噪声低至 7.8  $\text{nV}/\sqrt{\text{Hz}}$ ,完全符合本设计需求。

#### 2.2 前级电路滤波器设计

为了进一步减小 FPGA 端的计算压力,最大限度的减小高频噪声对系统的影响,在每一级放大器之间都需要插入滤波器,进一步增大输入信号的信噪比。

对于前级放大电路来说,滤波器通带到阻带的衰减应该足够快,才能保证更高的 SNIR。椭圆滤波器相较于其他滤波器结构,具有更加陡峭的过渡带,满足窄过度带和小阻带波动的需要。考虑到所采集的信号频率为1 MHz,将滤波器通带设置为15 MHz,以减小电感电容误差对滤波器所带来的影响,在滤除高频噪声的同时能保证通带的平坦度。最终滤波器的参数如图5 所示。

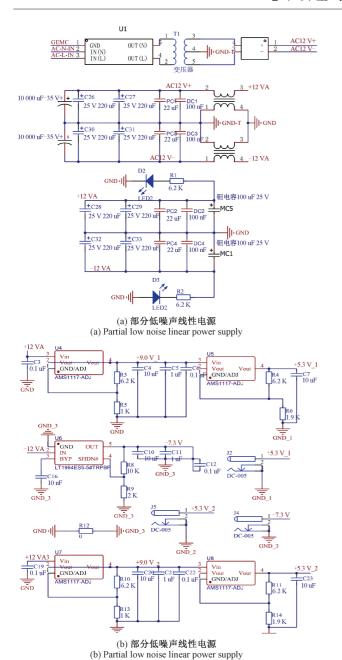

#### 2.3 低噪声电源设计

为了防止电源产生的纹波等噪声从电源,地回路等路径对系统产生影响,增大系统的噪声,所以需要对电源进行单独设计。常用的电源主要有两种类型:线性电源和开关电源。开关电源效率高,带负载能力强,但是在工作时内部的高频开关所产生的纹波会通过电流路径耦合到放大电路中,增大系统的噪声,从而影响检测。

线性电源主要通过变压器进行降压,实现稳定的输出,其工作原理比较简单,但是由于没有引入开关所以不存在纹波,而且噪声主要取决于器件,很适合用于微弱信号检测等领域,故设计都采用线性电源。本文所设计的电源如图 6 所示。

本文设计的低噪声线性电源采用变压器直接降压。市电先经过 EMI 模块进行滤波,有效的降低了市电的 EMI 辐射,提高了系统的稳定性和可靠性,再通过变压器 和整流桥进行降压和整流,实现正负 9 V 的输出。稳压电路采用两级 LDO 预稳压的结构,提高了每一级 LDO 的效率,避免 LDO 工作时效率不高发烫所产生热噪声,降低系统的噪声性能,同时增大了对于工频干扰的抑制。

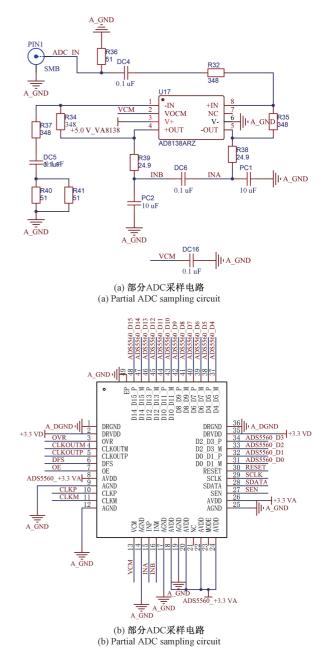

#### 2.4 ADC 采样电路设计

ADC 采样电路将前级低噪声放大电路所处理的信

图 6 低噪声线性电源 Fig. 6 Low noise linear power supply

号转换为数字信号,经 FPGA 读取并计算。ADC 采用 16 bits、40 M 采样率的高速差分输入 ADC,实际有效位数 达 13.5 位,SNR 达 84.3 dB,差分输入减小了高速 ADC 的 共模噪声,一定程度上改善了输入信号的信噪比。

ADC 的前级驱动电路采用低失真高速差分 ADC 驱动器。该芯片增益带宽积达 320 MHz,用于驱动差分输入 ADC。ADC 采样电路的主要电路如图 7 所示。

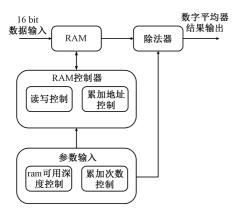

#### 2.5 数字平均器设计

由式(8)可知,数字平均器的原理是以周期性信号

图 7 ADC 采样电路 Fig. 7 ADC sampling circuit

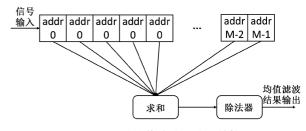

的重复周期 T 进行采样,每个周期采集到的数据为 N,将 采集到的每个周期数据进行相加再求平均,即可增大信 号的 SNIR。理论上相加的次数足够多,信号的 SNIR 就 无限大,可是由于测量系统和被测系统的时钟无法完全 统一,会在频率上存在微小的差别,当相加的次数过大 时,频率上微小的差别就会被慢慢放大,达不到增大系统 SNIR 的目的。数字平均器的程序结构如图 8 所示。

由式(8)可以计算得出对于信号的周期长度为 T,使用采样率为 fs 的 ADC 需要保存 N 个数据。系统使用 FPGA 的内部资源生成随机存取器 (random access

图 8 数字平均器程序结构

Fig. 8 Digital averaging program structure

memory, RAM),由于 FPGA 最多支持深度为 2 000 的二维数组初始化,所以为了保证电路的正常综合,需要控制 N<2 000。由式(8)可知,这也意味着只使用一个内部生成的 RAM,系统能够计算的最大脉冲的重复周期为 50  $\mu$ S。

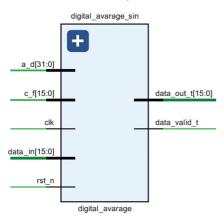

事先计算得出 RAM 深度与累加次数,输入到 RAM 控制器中。当数据输入时,将前 N 个数据依次保存到深度为 N 的二维数组中。当第 1 轮 N 个数据保存完毕之后,再将第 2 轮 N 个数据通过 RAM 读写控制器依次累加到对应的地址的 RAM 中。当累加次数与事先输入的累加次数相同时,再依次读出 RAM 中的数据,通过除法器取得平均值,得到的平均值即为数字平均的结果。数字平均器的接口界面如图 9 所示。

图 9 数字平均器接口界面

Fig. 9 Digital average interface

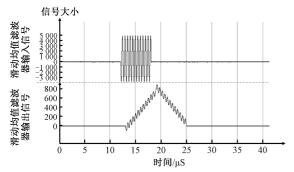

其中, clk 与 rst\_n 为系统时钟与复位, a\_d 为一个周期中数据的个数, c\_f 为积分次数, data\_in 为数据输入, data\_out\_t 和 data\_valid\_t 为数据输出和指示数据有效。数字平均器的仿真波形如图 10 所示。

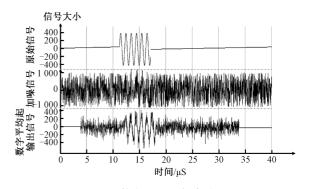

图 10 输入信号为峰值为 372 的周期短脉冲信号,周

图 10 数字平均器仿真波形

Fig. 10 Digital average simulates waveform

期 T 为 30 μS 由式(8)可以计算的每个周期的采样点数 为 1 200 个点。模拟白噪声由随机数生成,最大幅度为 1 000。叠加信号为输入信号与模拟白噪声相加,可以看 出来短脉冲信号已被完全淹没在了噪声里,肉眼无法分辨。将积分次数设为 20 次,从输出结果可以看出输入信号的信噪比明显提高。

#### 2.6 滑动均值滤波器设计

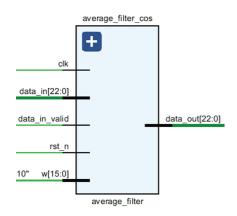

滑动均值滤波器本质上是一个低通滤波器,能一定程度保留信号的低频分量,对于脉冲信号而言,使用与输入脉冲宽度匹配的均值窗进行计算,可以准确定位到脉冲的位置并进行低通滤波。相较于一般的 FIR 滤波器,滑动均值滤波器在检测短脉冲时,对于 FPGA 的资源消耗少。数字均值滤波器的结构如图 11 所示。

图 11 滑动均值滤波器波器结构

Fig. 11 Moving mean filter wave structure diagram

滑动均值滤波器主要有 3 部分构成:移位寄存器,加 法器,除法器。数据先输入移位寄存器,当下一个数据到 来时,所有的数据右移,实现移位寄存器内数据的更新。 加法器根据当前输入的窗的大小,对前 M 个数据进行实 时求和,除法器主要对这 M 个数据进行平均,平均后的 数据就是滑动均值滤波器的输出。滑动均值滤波器的接 口如图 12 所示。

其中,clk 与 rst\_n 为系统时钟与复位,data\_in 与 data\_in\_valid 为混频后的信号输入与输入有效信号,W 为均值窗设置,为达到匹配脉冲的效果,W 设置应等于式(8)中的 N 。data\_out 为除法器的输出,即滑动均值滤

图 12 滑动均值滤波器接口

Fig. 12 Moving mean filter interface

波器的输出。滑动均值滤波器的仿真波形如图 13 所示。

图 13 滑动均值滤波器仿真波形

Fig. 13 Moving mean filter simulates waveform

由图 13 可以看出,对于输入滑动均值滤波器的短脉冲信号,当滑动均值滤波器的窗的大小和短脉冲信号的宽度匹配时,滑动均值滤波器能够准确的计算出短脉冲信号的低频直流分量,而对于短脉冲信号以外的信号输出的结果会急剧的衰减,克服了传统 FIR 滤波器在锁相放大器的应用中测量短脉冲信号建立时间不够的问题。

# 3 系统测试及结果分析

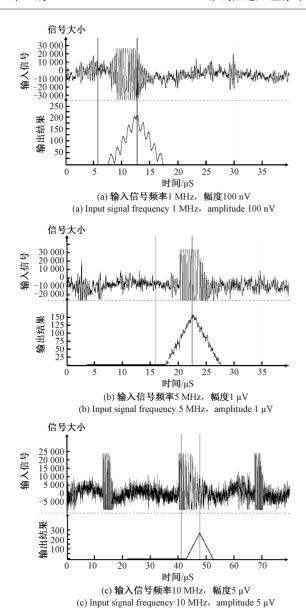

本实验采用射频微弱信号发生器产生微弱高频脉冲信号,通过在电脑端使用 FPGA 自带的内部逻辑分析仪(integrated logic analyzer,ILA)测量得到脉冲信号的幅度。搭建的实验平台如图 14 所示。

#### 3.1 频率测量性能与输入噪声测试

为了测试设备的频率特性,设置脉冲信号发生器发出重复周期为50 μS,脉冲宽度为5 μS 的短脉冲信号,根据式(8)可以算出一个周期需要采用的点数为2000个点。分别设置输入信号频率为0.6、1、2、5、10 MHz,通过改变输入信号幅度大小,观察时 FPGA 内部 ILA 的输出

图 14 系统实验平台 Fig. 14 System experiment platform

结果。部分结果如图 15 所示,具体频率与输入输出对照 如表 2 所示,根据测试结果计算得各个频率的线性度如表 3 所示。

表 2 系统输入与输出结果对照

Table 2 System input and output results comparison table

| 信号频率/ | 输入信号大小/μV |      |       |       |       |        |

|-------|-----------|------|-------|-------|-------|--------|

| MHz   | 0. 1      | 0. 5 | 1     | 2     | 5     | 10     |

| 0.6   | 178       | 685  | 1 384 | 2 700 | 6 742 | 13 910 |

| 1     | 219       | 970  | 1 924 | 3 731 | 9 144 | 17 793 |

| 2     | 117       | 488  | 914   | 1 865 | 4736  | 9 265  |

| 5     | 40        | 85   | 159   | 302   | 763   | 1 554  |

| 10    | 14        | 34   | 69    | 119   | 287   | 608    |

表 3 系统线性度 Table 3 Linearity of system

| 输入信号频率/MHz | 系统线性度    |

|------------|----------|

| 0. 6       | 0. 796 1 |

| 1          | 0. 814 9 |

| 5          | 0. 807 9 |

| 10         | 0. 790 1 |

| 30         | 0.7837   |

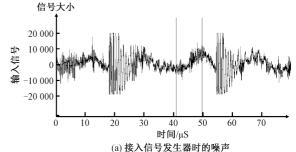

从图 15 可以看出输入信号上叠加了密集的高频噪声、一个频率大约 100 kHz 的低频噪声和偶发性的脉冲噪声。高频噪声主要是由微弱信号发生器内部的输出噪声、热噪声、信号传输过程中的环境噪声叠加而成。100 kHz 的低频噪声与偶发性的脉冲噪声主要来源是信号发生器的地噪声,当信号发生器接入系统时,低频噪声与脉冲噪声会通过地耦合进电路中,当设备与信号发生器断开连接时,噪声只有电路的本底噪声,此时 ADC 所采集到的噪声即为系统的底噪,如图 16 所示。根据式(7)可以算出信号发生器的耦合噪声经过放大电路放大后,幅度约为 0.95 V,已经完全将待检测的脉冲信号淹没。

由表 2 与 3 可以看出,对于频率在 0.6~10 MHz 的 输入信号,系统均能够准确识别,并且在各个频段均具有 良好的线性度。

图 15 部分系统输出结果 Fig. 15 Partial system output

由表 2 可以看出, 系统输出的幅度结果随着频率的增加呈现下降的趋势, 这是由于 ADC 采样率与带宽的限制。由于 ADC 的采样率为 40 MHz, 根据奈奎斯特定律, 所能不失真采集的信号为 20 MHz, 10 MHz 的输入信号已经接近了奈奎斯特定律的极限, 同样当输入信号频率越高, 就越接近系统的最大带宽, 导致采集的信号出现衰减。当系统的输入频率为 0.6 MHz 时, 由于射频低噪声放大器的低频性能的限制与通带内的增益波动, 实际增益比标准增益低, 没有工作在最佳频率, 放大后低频信号幅度略低于高频信号。由于 ADC 最终采集到信号幅度大小不一致的问题, 导致表 3 的线性度从低频到高频呈现先上升再下降的趋势, 但所能检测到的最小信号均能

(a) Noise when connect the signal generator

(b) Noise when disconnect the signal generator

图 16 接入与断开信号发生器时的输入噪声 Fig. 16 Input noise when connecting and disconnecting signal generators

达到 0.1 μV。

#### 3.2 脉冲长度测量性能测试

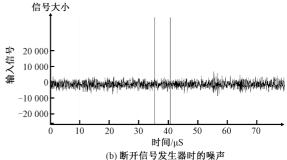

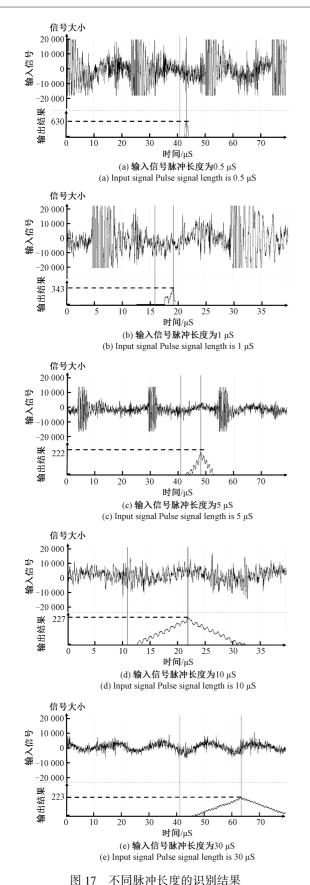

为了测试系统对不同脉冲长度的检测性能,设置信号发生器的输出频率为1 MHz,信号大小0.1 μV 信号重复周期为50 μS,分别测试脉冲长度为0.5、1、5、10、30 μS 时的输出结果。系统最终输出结果如图 17 与表 4 所示。

表 4 不同长度脉冲输入与输出关系

Table 4 Relation between input and output of pulse of different length

| 输入脉冲长度/μS | 系统输出结果 |

|-----------|--------|

| 0. 5      | 630    |

| 1         | 343    |

| 5         | 222    |

| 10        | 227    |

| 30        | 223    |

由表 4 可知, 当输入脉冲长度为 5~30 μS 时, 系统的输出结果与表 2 误差在 10 个 LSB 以内。当输入脉冲的长度为 0.5 μS 与 1 μS 时, 误差较大。原因是当输入脉冲信号的持续时间小于或者接近原始信号的一个周期时, 原始信号不是一个完整的周期。残缺的信号经过锁相放大器后不能有效的检测出信号的幅度, 导致误差较大。

#### 3.3 测试总结

由表 2~4 可知,对于该方法而言,影响检测

Fig. 17 Recognition results of different pulse lengths

信号频率范围和线性度的主要是前级低噪声放大器的最佳工作频率与 ADC 的采样率和带宽,当信号的频率远小于 ADC 的最大带宽和奈奎斯特频率,并且在该频率放大器工作在合适的增益范围时,在该频段就具有良好的线性度。

影响系统能检测最大的脉冲长度和重复周期的主要是数字平均器中 ram 的深度,在资源足够的情况下,ram 越深,系统能检测的脉冲就越长。系统能检测的最短的脉冲长度主要受制于待检测信号的最小周期,当输入的信号周期大于待检测脉冲长度时,这个信号就不是一个完整的信号,此时锁相放大器就有较大的误差。

# 4 结 论

针对高频非线性超声微弱短脉冲信号的检测,本研究在传统的锁相放大基础上,研究了一种新的锁相放大技术。通过分析传统锁相放大器对于微弱短脉冲信号检测存在的不足之处,结合超声信号周期性的特点,对数字锁相放大器与前级处理电路进行的改进。在传统的锁相放大器混频之前增加数字平均,并且在前级处理电路都使用了低噪声器件,电源处使用线性电源,减少了外部噪声的影响,克服了输入信号噪声较高的问题,增大了输入信号的信噪比。将锁相放大器后级的低通滤波器替换为滑动均值滤波器,实现了低通滤波和脉宽匹配,避免了低通滤波器对脉冲信号建立时间不够的问题。实验测试结果表明,该系统能够准确的在强噪声中检测到淹没在其中的微弱脉冲信号。

该研究为其他研究者提供了一种新的锁相放大器架构思路,通过对锁相放大器架构的创新,为相关领域的研究,特别是超声无损检测、非稳态信号处理等领域的应用提高了重要参考。在未来的工作中,研究者会继续研究有关微弱非连续信号的测量与提取,通过继续改进锁相放大器的架构,考虑结合人工智能的数据预测加入锁相放大器架构中,以此来检测其他类型的非连续信号。

### 参考文献

- [1] 赵龙,王鑫,罗大程,等. 基于金刚石氮-空位色心的裂纹 无损检测[J]. 电子测量与仪器学报,2022,36(7):239-246.

- ZHAO L, WANG X, LUO D CH, et al. Nondestructive crack detection based on diamond nitrogen-vacancy color center [J]. Chinese Journal of Electronic Measurement and Instrumentation, 202, 36(7);239-246.

- [2] 魏丞耀, 王雪梅, 倪文波, 等. 衬胶管道脱粘缺陷超声检测与识别方法研究[J]. 电子测量技术, 2024, 47(1):23-30.

- WEI CHY, WANGXM, NIWB, et al. Research on

- ultrasonic detection and identification method of disadhesion defects of rubber lined pipeline [ J ]. Electronic Measurement Technology, 2024, 47(1); 23-30.

- [3] 尹昱, 陈振华, 肖峰, 等. 不锈钢疲劳微损伤的非线性超声检测方法[J]. 电子测量与仪器学报,2020,34(1):68-73.

- YIN Y, CHEN ZH H, XIAO F, et al. Nonlinear ultrasonic detection method for fatigue microdamage of stainless steel [J]. Journal of Electronic Measurement and Instrumentation, 2020, 34(1):68-73.

- [4] 郭忠凯, 李永刚, 于博丞, 等. 锁相放大器的研究进展[J]. 物理学报,2023,72(22):132-150.

GUO ZH K, LI Y G, YU B CH, et al. Research progress of phase-locked amplifiers [J]. Acta Physica Sinica,2023,72(22):132-150.

- [5] 阴欢欢, 李飞, 严鑫. 自适应校相的锁定放大器设计[J]. 电子测量技术,2015,38(8):30-35.

YIN H H, LI F, YAN X. Design of locking amplifier for adaptive phase calibration [J]. Electronic Measurement Technique,2015,38(8):30-35.

- [ 6 ] DE MARCELLIS A, PALANGE E, LIBERATORE N, et al. Low-cost portable 1 MHz lock-in amplifier for fast measurements of pulsed signals in sensing applications[J]. IEEE Sensors Letters, 2017, 1(4): 1-4.

- [7] DE MARCELLIS A, PALANGE E, STANCHIERI G D

P, et al. Portable lock-in amplifier-based optoelectronic

readout circuit for high-sensitivity differential measurements

of laser pulse energy variations [J]. Journal of Low Power

Electronics, 2019, 15(1): 87-94.

- [8] 邓冬梅, 邵明珍. 锁相放大技术在大学光谱实验教学中的应用[J]. 物理与工程,2023,33(3):76-79,87.

DENG D M, SHAO M ZH. Application of phase-locked amplification technique in spectral experimental teaching inuniversities [J]. Physics and Engineering, 2023, 33(3):76-79,87.

- [9] 张雷雷,曹振松,钟磬,等. FPGA 主控型数字锁相放大器设计及光谱测量[J]. 红外与激光程,2023,52(10):135-146.

ZHANG L L, CAO ZH S, ZHONG Q, et al. Design and spectral measurement of digital phase-locked amplifier based on FPGA[J]. Infrared and Laser Engineering, 2023,52(10):135-146.

- [10] 刘慧芳. 用于红外激光气体检测的数字正交锁相放大器的研制[D]. 长春:吉林大学,2017.

LIU H F. Development of digital orthogonal phase-locked amplifier for infrared laser gas detection [D].

Changchun: Jilin University,2017.

- [11] 李国林, 蒋庆志, 马坤, 等. 基于 CIC 的数字正交锁

- 相放大器的甲烷检测实验研究[J]. 光子学报,2021,50(2):130-141.

- LI G L, JIANG Q ZH, MA K, et al. Experimental study on methane detection using a digital orthogonal lock-in amplifier based on CIC  $[\ J\ ]$ . Acta Photonica Sinica, 2021,50 (2):130-141.

- [12] 陈稳稳. 基于 FPGA 的数字正交锁相放大器研制及气体检测应用[D]. 长春:吉林大学,2021.

CHEN W W. Development and gas detection application of digital orthogonal phase-locked amplifier based on FPGA [D]. Changchun; Jilin University,2021.

- [13] 苑效宁, 马少华, 董鹤楠. 数字锁相放大器的算法设计与优化[J]. 东北电力技术,2022,43(1):41-44,49. YUAN X N, MA SH H, DONG H N. Algorithm design and optimization of digital phase-locked amplifier [J]. Northeast Electric Power Technology, 2022, 43(1):41-44,49.

- [14] 杨保海,任全会,李海生.基于 SOPC 数字锁相放大器设计与实现[J].电子器件,2021,44(3):535-538. YANG B H, REN Q H, LI H SH. Design and implementation of digital phase-locked amplifier based on SOPC [J]. Electronic Devices,2021,44(3):535-538.

- [15] 赵宇红, 王帝, 王艳蓉, 等. 一种用于数字锁相放大器的改进 Goertzel 算法 [J]. 电子世界, 2019 (23): 5-7,13.

ZHAO Y H, WANG D, WANG Y R, et al. An improved Goertzel algorithm for digital phase-locked amplifiers [J]. Electronic World, 2019 (23): 5-7,13.

- [16] 汪少锋. 基于 FPGA 带频率自适应跟踪的矢量型数字锁相放大器设计[D]. 武汉:华中科技大学,2016. WANG SH F. Design of vector-type digital phase-locked amplifier with frequency adaptive tracking based on FPGA [D]. Wuhan: Huazhong University of Science and Technology,2016.

- [17] 谢桂辉, 郑旭初, 赵天明, 等. 基于 FPGA 的便携式 正交锁相放大器研制[J]. 电子技术应用, 2018, 44(10):78-82,87.

XIE G H, ZHENG X CH, ZHAO T M, et al. Development of portable orthogonal phase-locked Amplifier based on FPGA[J]. Application of Electronic Technique, 2018,44(10):78-82,87.

- [18] 闫庆, 高丰佳, 徐鑫鑫, 等. 非同轴激光雷达重叠因子的自校正系统设计[J]. 仪器仪表学报, 2023, 44(7):315-324.

YAN Q, GAO F J, XU X X, et al. Design of self-correcting system for non-coaxial Lidar overlap factor[J].

Chinese Journal of Scientific Instrument, 2023, 44(7): 315-324.

- [19] 付苗苗, 刘娜. 激光雷达信号检测系统的最佳匹配滤波方法[J]. 激光杂志,2023,44(10):194-199.

- FU M M, LIU N. Optimal matching filter method for LiDAR signal detection system [J]. Laser Journal, 2023, 44(10):194-199.

- [20] 魏志坤. 微弱电流信号调理和采样硬件电路实现[D]. 成都:电子科技大学,2022.

WEI ZH K. Implementation of hardware circuit for weak current signal conditioning and sampling [D]. Chengdu: University of Electronic Science and Technology of China, 2022.

#### 作者简介

**谢子成**,2022 年于长沙理工大学获得学士学位。现为长沙理工大学硕士研究生,主要研究方向为微弱信号检测与数字信号处理。

E-mail: 2410630814@ qq. com

Xie Zicheng received his B. Sc. degree from School of Physics and Electronic Science, Changsha University of Science and Technology in 2022. Currently, he is a M. Sc. candidate at Changsha University of Science and Technology. His main research interests include weak signal detection and digital signal processing.

唐立军(通信作者),教授(二级),博士,博士生导师,湖南省优秀教师,长沙理工大学教学名师,湖南省电子学会副理事长,湖南省物理学会副理事长、中国电子教育学会研究生教育分会理事。1986年毕业于湘潭大学物理系,获学士学位,1989年毕业于

中国科学院上海原子核研究所获硕士学位,2003 年毕业于中国科学院上海原子核研究所获工学博士学位,主要研究方向为智能感知与信号检测。

E-mail: tanglj2009@ 163. com

Tang Lijun (Corresponding author), professor (Grade II), Doctor, doctoral supervisor, excellent teacher of Hunan Province, famous teacher of Changsha University of Science and Technology, Vice chairman of Hunan Electronics Society, vice chairman of Hunan Physics Society, director of Graduate Education Branch of China Electronic Education Society. He received his B. Sc. degree in physics from Xiangtan University in 1986, M. Sc. degree from Shanghai Institute of Nuclear Research, Chinese Academy of Sciences in 1989 and Ph. D. degree in engineering from Shanghai Institute of Nuclear Research, Chinese Academy of Sciences in 2003. His main research interests include intelligent perception and signal detection.