DOI: 10.13382/j. jemi. 2017. 05. 008

# 基于以太数据的无线激光通信系统透明传输设计\*

亢 烨 柯熙政 邱昌佩

(西安理工大学 自动化与信息工程学院 西安 710048)

摘 要:以太网数据的透明传输是在传输过程中对外界透明,不用关心下层协议,只负责将需要传送的业务数据传送到目的节点,而不篡改数据内容、不改变数据属性的一种传输方式。采用以太数据透明传输的无线激光通信系统,可以方便的与现有工业以太网络无缝集成,提高设备可用性,扩大其应用范围。基于 DE2-115 教育开发平台,利用板载 FPGA 集成 Nios II 软核作为控制单元,运行裁减后的 NicheStack TCP/IP 协议栈的  $\mu$ C/OS II 实时操作系统,实现了无线激光通信系统与千兆以太网在数据链路层上的数据透明传输。通过系统仿真、电路实验以及光路实验对本设计进行了数据一致性测试。测试结果表明,本设计具有良好的数据透明传输特性。

关键词:无线激光通信;以太网透明传输;Nios II 软核处理器;μC/OS II

中图分类号: TN929.1; TP321 文献标识码: A 国家标准学科分类代码: 510.20

# Design of data transparent transmission in WLC system based on ethernet

Kang Ye Ke Xizheng Qu Changpei

(Faculty of Automation and Information Engineering, Xi'an University of Technology, Xi'an 710048, China)

Abstract: Transparent transmission is one method of transferring Ethernet data so that it is only responsible forsending business data to destination nodes without regard for the underlying protocol or preprocessing of data properties and content. The program uses Nios II, which is integrated into field programmable gate arrays as the control element. By transplanting  $\mu$ C/OS-II real-time operating systems, using NicheStack TCP/IP protocol stacks, packets were captured and forwarded on the data link layer transparently between wireless laser communication system and the Ethernet. The data consistency of the design is tested by system simulation, circuit experiment and optical experiment. Our test results showed that the scheme performed transparent transmission well.

Keywords: wireless laser communication; ethernet transparent transmission; Nios II soft core processor; μC/OS II

# 1 引 言

利用激光束作为信号载体,在空间(陆地或外太空)直接进行语音、数据、图像等信息传送的无线激光通信技术凭借其传输速率高,安全保密性好,抗电磁干扰能力强等特点近年来逐步走向实用化。美国的 Terra 公司、日本Hamamatsu、Sony 和佳能等公司也都相继推出过一些实用化程度高的无线激光通信产品,传输速率涵盖25~622Mbps<sup>[1]</sup>。国内主要是中国电子科技集团公司第

三十四研究所、上海光学精密机械研究所、武汉大学、西安理工大学等单位在无线激光通信产品上进行研究并上取得了多项成果<sup>[27]</sup>。

但在无线激光光通信网络与工业以太网无缝业务衔接方面,各方都一直在寻找好的解决方案。比如,文献[8]提出了一种在 SAMSUNG S3C44BOX 微处理器运行嵌入式 μClinux 的系统上通过 Socket 编程实现了网络通信,但该方案受限于 RTL 9019s,仅能进行 10 Mbps 以下的以太网数据传输,难以适应高数据量传输要求。文献[9]提出了一种基于 Altera 公司 Cyclone 系列 FPGA 内

收稿日期:2017-03 Received Date: 2017-03

<sup>\*</sup>基金项目:国家自然科学基金(61377080,60977054)资助项目

嵌有 Nios II CPU 的设计,实现了一种利用套接字来收发数据以太网控制器设计。在数据链路层使用套接字来收发网络数据,这样会涉及源 IP 地址、目的 IP 地址、源端口号和目的端口号等诸多问题,导致网络数据后续处理复杂,使用不便。文献[10]介绍了一种从链路层和物理层实现了 Ethernet 网上透明传输的基本方法,受限制的是该方案是在 Linux 操作系统下实现的。文献[11]提出一种使用 ARM v7 处理器的嵌入式网络解决方案,但这种方案对处理器的运行速度和存储容量要求很高。

本文设计了一种基于  $\mu$ C/OS II 和嵌入式 Nios II 软核的以太数据透明传输方案,将之应用于无线激光通信的数据链路层通信中,实现其与工业以太网的数据包透明传输。该设计采用 DE2-115 硬件开发平台作为基础,使用高性价比的 FPGA 配合千兆以太网 PHY 芯片,利用 Quartus II 工具在 Nios II 基础上进行开发,在嵌入式实时操作系统  $\mu$ C/OS II 运行精简的 NicheStack TCP/IP 协议栈实现网络底层驱动的控制,在无线激光通信的数据链路层上实现了千兆以太数据的透明传输。经过实测验证,证明该方案简便可行。

### 2 以太数据透传原理

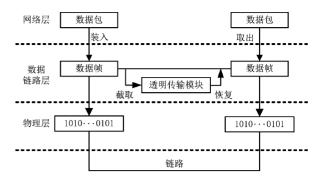

为了实现与工业以太网的互联互通,无线激光通信网络接口的实现也参照了开放式系统互联 OSI 的 7 层模型,按照不同的任务功能由下至上将其划分为物理层、数据链路层、网络层及传输层等 7 层,每一层完成相应的一项任务,并对紧邻的上层数据包一并进行封装,构建自己层的数据包又送人紧邻的下一层进行处理。对于无线激光通信网络来说,物理层就是建立激光器与光电探测器之间的光信号物理连接,而数据链路层就是为了实现通过单一光信号链路传输数据所进行的数据包调制和解调。本文通过对送入激光器的数据进行编码,对光电探测器接收到的光信号数据包进行过滤解码恢复,就能在由激光信号构建的物理层的无线激光通信系统的数据链路层上严格实现 Ethernet 数据的透明传输。数据链路层的透明传输的原理如图 1 所示。

在 OSI 模型的数据链路层,Ethernet 数据默认是通过向一个冲突域内所有的节点进行广播数据包的方式来进行信息传输的,且只有与广播数据包中的目标 MAC 地址一致的网卡才能正确接收数据包。而打造无线激光通信的透明传输,就是在冲突域中在加入两条隐形节点,实现将有线网络接收到 Ethernet 数据包不对其数据帧内容做任何修改的使用激光器发至一端的光电探测器,探测端又将该 Ethernet 数据包的数据帧内容还原成包含目标网络节点 MAC 信息的数据包,并透过网络接口发出,从而实现无线激光网络的透明传输。

图 1 数据链路层透明传输原理

Fig. 1 Schematic of transparent transmission of data link layer

### 3 透明传输硬件系统

#### 3.1 实时操作系统前段后不空

整个无线激光数据透明传输系统需要完成千兆以太 网接口数据处理,激光信号高速编解码等任务,因此需要 既可以保证这几项任务能够互不干扰的独立高速进行, 又能够很容易的实现准确无误的实时操作,同时还应具 有二次实时应用程序开发难度适中,可扩展行强等特点。 为此,我们选用基于优先级的抢占式多任务实时操作系 统 μC/OS II,它具有实时内核、任务管理、中断管理、任务 间通信同步(信号量,邮箱,消息队列)和内存管理等基 本功能,同时也具有我们看中的良好的可移植性和可裁 剪性。

#### 3.2 Nios II 软核处理器

选用 Altera 公司的第二代通用 32 位 RISC 软核 CPU—Nios II 来作为运行 µC/OS II 的基础配置底层核 心平台。软核 CPU 的优势在于设计者可以在不影响已有的软件投入<sup>[12]</sup>的前提下,根据系统需求的变化来更改 CPU 的类型,从而选择满足高性能和低成本的最佳方案。因为 Nios II 软核系列既包括系统性能高、FPGA 资源占用适中的快速型产品 Nios II/f,也包括高性能、低 FPGA 资源使用量的标准型产品 Nios II/s,甚至还有低性能但 FPGA 资源使用量同样经济的经济型产品 Nios II/e;最关键的一点是他们具有相同的 32 位处理器基本结构单元,具有相同的指令集架构(ISA),完全兼容的二进制代码,选用的唯一标准就是应用需求<sup>[13]</sup>。

#### 3.3 硬件平台

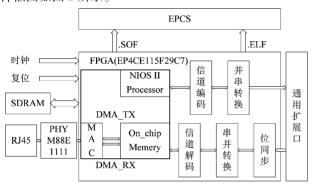

系统软件主要由 Nios II 处理器模块、编解码模块、 并串转换和串并转换模块、位同步即时钟数据恢复模块 组成,所以强大的硬件资源是选择该开发基础平台的关 键因素。基于以上的系统软件需求,选用友晶科技的 DE2\_115 教育开发平台,因为该开发板的主 FPGA 采用 Altera 公司 EP4CE115F29C7,拥有 114 480 个逻辑单元, 4 329 K内存块,3888K Bits 片上存储单元,以及 4 个 PLL 单元,资源十分丰富。

选用 DE2\_115 开发板的第二个原因在于这块板子同时具有两个 Marvell 公司的 88E1111 以太网 PHY 芯片,这样就可以用两块以太网 PHY 芯片分别模拟不同的网络接口从而在同一块开发板上进行两个网络设备之间的联合调试,简化了开发过程。

DE2\_115 开发板提供了 2 片 64MB 的 SDRAM 作为外部存储器,完成程序的运行和数据的存储等相关功能。并且有 EPCS64 作为主动串行配置芯片,完成程序的断电上电加载功能。与此同时,该款开发板还有着不同频率的晶振用来提供不同需求的时钟源。本设计的系统硬件框图如图 2 所示。

图 2 系统硬件框图

Fig. 2 Design of the system hardware block diagram

#### 3.4 片上系统设计

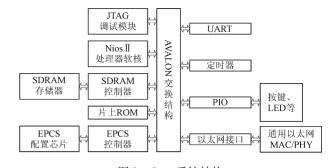

本设计使用 Qsys 系统提供的 Triple Speed Ethernet MegaCore 的 IP 核组件作为千兆以太网透明网络传输的开发基础。其中50 MHz 主时钟信号,以及125 MHz 以太网信号接收时钟信号是通过板载晶振产生,并且分别通过 FPGA 内建的多个 PLL 电路为其他硬件电路提供所需的时钟信号;利用片上存储资源,构建 FIFO、以太网数据缓存区以及紧耦合数据/指令存储器等各种片上存储器;利用 SGDMA 组件完成数据从 FIFO 队列到数据缓存区,再到 MAC 之间的传输,用以减少 CPU 的资源占用;利用 SDRAM 控制器实现了控制组件与外部的 SDRAM 芯片的连接,可以提供足够的程序运行和数据堆栈的资源空间;利用 PIO 组件实现对外围通用 IO 口的控制;通过 Avalon 总线完成 IP 组件的互连,组件地址的分配与中断优先级的设置,最终生成 Qsys 系统[14]。本设计的 Qsys 系统结构如图 3 所示。

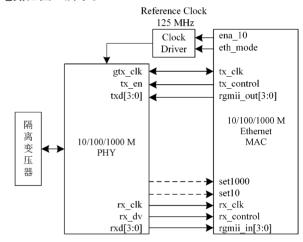

#### 3.5 以太网接口模块设计

为了实现激光链路透明传输以太网数据的目的,可根据开发板提供的 Marvell 公司的 88E1111 型 PHY 芯片构建以太网接口以完成 IP 层数据包的组帧和解帧。选

图 3 Qsys 系统结构

Fig. 3 Qsys system configuration diagram

择常用的 1 000 Mbps 全双工模式 MAC 核,通过 RGMII 方式的 MAC 层接口与 PHY 连接,使之具有 10/100/1 000 M自适应数据传输能力<sup>[15]</sup>。本设计的 RGMII 接口电路如图 4 所示。

图 4 RGMII 接口电路

Fig. 4 Design of GRII Interface

# 4 软件模块设计

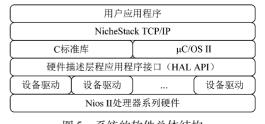

本设计基于 Nios II CPU 系统进行软件开发,需要使用 Nios II EDS 开发环境。根据 Nios II 系统的架构,在其基础上实现 NicheStack TCP/IP 协议栈,实现对以太网的控制和数据透明传输,在 BSP 文件生成的时候,加入  $\mu$ C/OS II系统和 NicheStack TCP/IP。Nios II 系统的软件框架总体结构如图 5 所示。

图 5 系统的软件总体结构

Fig. 5 The framework of the Nios II system

#### 4.1 初始化网卡接口

NicheStack TCP/IP 协议栈的主要接口是一个标准的套接字接口,在使用的时候,需要用到这个系统初始化任务 SSSInitialTask(void \* task\_data)。这个任务函数在main()函数中被创建,主要用来初始化 NicheStack TCP/IP 协议栈以及创建用户的其他任务和创建操作系统的数据结构,这个任务在所有的任务中优先级别最高。

任务完成后,需要调用 OSTaskDel (OS\_PRIO\_SELF) 使其进入休眠态,这样就不被操作系统调用了。因此,用户还需要调用以下两个函数即 alt\_iniche\_init()和 netmain(),前一个函数用来初始化协议栈,后者用来初始化 NicheStack 并触发系统任务<sup>[9]</sup>。

初始化协议栈完成后,将一个全局变量 iniche\_net\_ready 置为 1。此外,用户必须提供两个函数 get\_mac\_addr()和 get\_ip\_addr(),用以系统获得开发板的 mac 地址和 IP 地址。

最后,在 main()函数中调用 OSStart()来启动  $\mu$ C/OS II 的任务调度函数,这样就完成了系统的初始化任务。

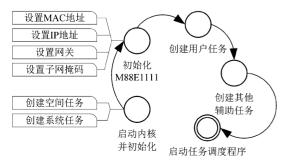

#### 4.2 实时内核 μC/OS II 的任务调度程序

$\mu$ C/OS II 提供了任务管理的各种函数调用,包括创建任务,删除任务,改变任务的优先级,任务挂起和恢复等。系统初始化时会自动产生两个任务:一个是空闲任务,它的优先级最低,该任务仅给一个整形变量做累加运算;另一个是系统任务,它的优先级为次低,该任务主要负责统计当前 CPU 的利用率,系统初始化完成之后,复位并设置 M88 E111 的各种寄存器,完成 M88 E111 的初始化工作;创建用户任务,并设置合适的优先级,监测网络连接和数据传输请求并且设置合适的优先级,创建其它所需的辅助功能任务并设置合适优先级。 $\mu$ C/OS II的初始化是通过调用系统函数 OSInit()实现的。多任务的启动是通过调用 OSStart(),实现从任务就绪表中找出用户建立的优先级最高的任务控制块。需要特别指出的是,在启动  $\mu$ C/OS II 之前至少要建立一个应用任务。实时内核  $\mu$ C/OS II 任务调度工作流程如图 6 所示。

图 6 实时内核 μC/OS II 任务调度工作流程 Fig. 6 Working flow of Real Time Kernel

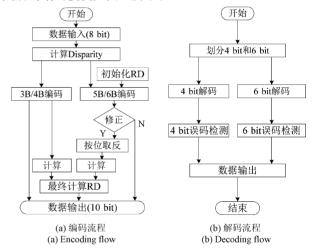

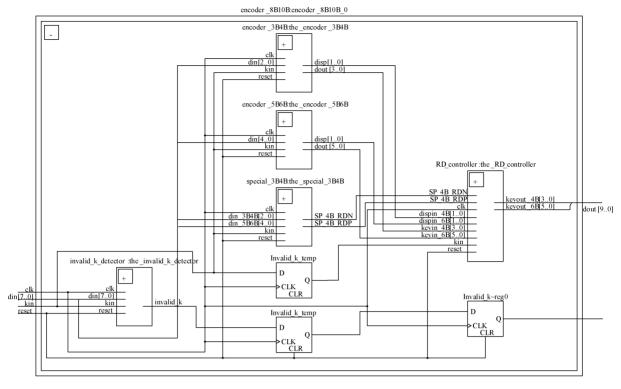

#### 4.3 8B/10B 信道编解码

为了减小数字信号在信道传输时受噪声等影响所引起的差错,需在发射机中对信源信息按一定的规则进行抗干扰编码,并在接收端接收到该信号后按照逆规则进行解码恢复,这一过程有助于提高系统的通信可靠性。

为了实现激光链路与千兆以太网络对接,本设计采用了8B/10B的信道编码。这种编码最大的特点就是直流平衡,即码元"0"和码元"1"数量保持基本一致,因为这种编码机制使用两个10 Byte 字符来表示8 Byte 字符,保证每5个连续的"1"或"0"后插入一位"0"或"1",从而保证不平衡度不大于1。同时,为了确保同步定位的准确,在编码中还采用了只存在于控制字符(K28.5,K28.1,K28.7)中的特殊字符[16]。

通过8B/10B编码,既可以保证传输的数据串在接收端被正确复原,又可以利用一些特殊的代码提高解码效率,并提早发现数据位传输错误,抑制误码<sup>[17]</sup>。给出8B/10B编解码的流程如图7所示,使用Verilog综合工具后的编码模块如图8所示。

图 7 8B/10B 编解码流程

Fig. 7 Flow Chart of 8B/10B Encoding & Decoding

#### 4.4 位同步模块

在数据通信中,最基本的同步方式就是位同步(bit synchronization)或者是比特同步,比特是数据传输的最小单位,位同步是指接收端时钟已经调整到和发送端时钟完全一样,位同步的目的就是要在正确的时刻(通常是在每一位的中间时刻位置)对收到的电平根据事先已经约定好的规则进行判决,若电平超过一定的门限阈值则为1,否则为0。

位同步方法为利用 FPGA 内部锁相环产生  $N \times f$  的高频时钟并根据输入信号对其分频,从而产生同步时钟信号实现位同步,其中 N 决定了恢复时钟信号的相位精度 [18],通常 N=8。本设计利用 10 倍频的方法对数据进行采样,

图 8 8B/10B 编码电路模块

Fig. 8 Synopsys of 8B/10B Encoding Modules

利用 120 MHz 的时钟恢复出发送端 12 MHz 的时钟,并且根据采样数据分析判断出数据条边沿的位置,找到最佳采样时钟,根据最佳采样位置恢复出数据。根据倍频法的原理,利用 Verilog 语言描述了一种数据时钟恢复的电路,CLK120 为数据时钟恢复模块的输入时钟,发送端的发送时钟为 12 M,利用 10 倍频,ClkRec 为恢复出来的发送时钟,ClkIn 为数据时钟恢复的输入,CodeOut 为恢复出的发送端的数据,输出的数据和输入的数据一致,并且延迟了一个时钟周期,恢复出来的发送时钟为 12 M,和发送端的时钟吻合,可以看出该模块成功的恢复了时钟以及数据。

### 4.5 串并转换与并串转换

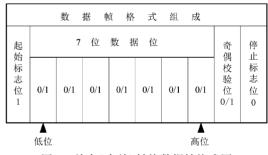

调制电路需要对数据按位进行处理,因此发送端对数据需要进行并串转换,而接收端则需做逆转换,即将串行的数据转换成并行的数据送入解码模块[19]。本设计在并串转换和串并转换过程中采用的数据帧格式如图9所示。利用 Verilog 描述该功能模块,为了测试正确性,将并串转换和串并转换的两个模块接在一起,利用内置的示波器进行仿真,表明正确实现了并串和串并转换。

# 5 实验结果

#### 5.1 串并转换与并串转换

本文所有的设计都是在 DE2\_115 开发板上实现的,

图 9 并串(串并)转换数据帧格式图

Fig. 9 Frame Data format of Serializer (Deserializer)

从 Quartus II 生成的编译报告中可以得到硬件的资源使用情况,表 1 所示的就是本次设计的资源使用情况。

表 1 硬件资源使用情况 Table 1 Resources Usage Statistics

| Logic Utilization                  | Utilization        |

|------------------------------------|--------------------|

| Total logic elements               | 11743/114480(10%)  |

| Total combinational functions      | 8970/114480(8%)    |

| Dedicated logic registers          | 8539/114480(7%)    |

| Total registers                    | 8618               |

| Total pins                         | 123/529(23%)       |

| Total virtual pins                 | 0                  |

| Total memory bits                  | 189866/3981312(5%) |

| Embedded multiplier 9-bit elements | 4/532( <1% )       |

| Total PLLs                         | 2/4(50%)           |

#### 5.2 结果测试

将硬件工程即 Quartus II 生成的. sof 文件和 Nios II EDS 生成的. elf 文件下载到 EP4CE115F29C7 开发板中,通过对 FPGA 编程控制串口来显示操作系统的运行情况,比如协议栈的初始化信息、获取的 IP 信息和 MAC 地址信息。

#### 5.2.1 线缆链路实验测试

线缆链路上数据正确传输是无线激光通信链路传输 正确的第一步。因为电路实验相当于一个无大气湍流干扰、不需要考虑光路功率衰减,对准等一系列实际问题的 理想链路。

用 2 台 PC 各自通过以太网口与开发板相连做为数据的发送端和接收端,两个开发板使用千兆以太网线缆进行连接搭建线缆链路实验测试平台。实验效果如图 10 所示。

图 10 线缆链路实验测试平台

Fig. 10 Demonstration of Cable Link Testing Platform

测试网络通信的可通性。设置 PC 机 A 的 IP 地址为 192.168.0.3, 而 PC 机 B 的 IP 地址为 192.168.0.10; 在 PC 机 A 的命令行控制程序使用 ping 命令发送数据包检测 PC 机 A 到 PC 机 B(ping 192.168.0.10 -t), 在 PC 机 B 上 使用 ping 命令(ping 192.168.0.3 -t)发送数据包至 PC 机 A,经过测试说明系统在数据链路层是通信正常。

使用网络调试助手软件来检验系统的通畅性和数据 传输的完整性。在两台 PC 终端上同时使用网络调试助 手向对端发送数据,经过对比两端接收和发送,发现数据 完全一致,并且实现了双工通信。说明该系统在电路上 透明传输数据是完全可行的。

#### 5.2.2 激光链路实验测试

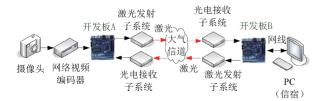

搭建无线激光链路数据透明传输系统以验证本设计 的正确性。搭建实验光路的示意图如图 11 所示。发射

图 11 激光链路实验示意图

Fig. 11 Demonstration of Laser Link Experiment

一端利用接上高清视频摄像头的视频网络服务器产生 持续的网络数据码流,接收一端则使用电脑进行数据 接收。

在发送端,利用已有的设备将信源数据打包成标准的网络数据包,经过 RJ-45 接口输送至嵌入在 FPGA 内部的 Nios II 软核里,搬运数据至双时钟 FIFO 里,进行8B/10B 信道编码,并串转换输送至激光调制电路,并且加载到激光器上发送至大气信道中。接收端光电探测器接收光信号经过光电转换,在 FPGA 内部进行时钟恢复,并串转换,10B/8B 信道解码,并将数据通过 Nios II 发送至网卡,完成接收过程。

UDP 数据包透明传输测试使用 Wireshark 作为发包工具,利用 PC 端网卡发送原始数据包,经以太网网络传输到开发板,经过激光调制电路送至激光链路,经激光链路传输后由接收端接收,收到后在发送至 Wireshark 运行的 PC 端。Wireshark 抓到的数据包是两条,其中一条是发包工具发给开发板的,另一条是该数据经过系统,开发板返还给电脑的数据包,将这两条数据包拆解开来,对比数据,发现数据帧完全一致,数据包没有任何的修改,这就说明了该系统成功的实现了网络数据的透明传输。证明了该系统的正确性和可行性。

### 6 结 论

本文设计了一种无线激光千兆以太数据透明传输模块,采用 FPGA 和千兆以太网 PHY 芯片作为硬件平台,通过在 Nios II 上搭建实时操作系统 μC/OS II 并嵌入 NicheStack TCP/IP 协议栈的处理方式,在实现了千兆以太数据在无线激光链路上的透明传输。通过仿真,线缆链路实验与光路实验,利用网络数据提取工具,分别对通过线缆链路接收到的数据以及通过无线激光通信链路传输后接收到的数据与发送的原始数据进行一致性比对,验证了本系统在硬件和软件的可行性以及实现了基于无线激光数据链路层的透明传输功能,验证了本系统在硬软件上的可行性以及实用性。

#### 参考文献

- [1] 林伟,马新香. 便携式光通信综合测试仪的研制[J]. 国外电子测量技术,2015,34(5):43-47.

- LIN W, MA X X. Development of a portable optical telecommunication integrated tester [ J ]. Foreign Electronic Measurement Technology, 2015, 34 (5): 43-47

- [2] 刘立人. 卫星激光通信研究进展[J]. 科学:上海, 2007, 59(3):29-33.

- LIU L R. International developments in laser communications [J]. Science: Shanghai, 2007, 59(3):

[4]

[5]

[7]

- 29-33.

- [3] 袁强, 陈旭辉, 王志勇. 无线激光通信技术的实际应用[J]. 信息通信, 2007(4):17-20.

YUAN Q, CHEN X H, WANG Z Y. Information & Communications, 2007(4):17-20.

张鹏,王天枢,杨国伟,等.全双工逆向调制回复空

- 间光通信系统性能评价[J]. 红外与激光工程, 2015, 44(8):2506-2510.

ZHANG P, WANG T SH, YANG G W, el al. Performance evaluation of full-duplex free space laser communication system based on modulating retroreflector[J]. Infrared and Laser Engineering, 2015, 44(8):2506-2510.

- 统研究与实现[J]. 激光与红外, 2016, 46(10):1220-1224.

ZHONG K, HE N, JIANG H Y. Research and implementation of data transmission in laser communication system with variable fundamental frequency[J]. Laser and Infrared, 2016, 46(10):1220-1224.

钟坤,何宁,蒋红艳.可变基频激光通信数据传输系

- [6] 涂巧玲, 胡涛, 曹阳. 机载激光通信终端的模糊变结构跟踪方法研究[J]. 半导体光电, 2015, 36(1):125-127.

TU Q L, HU T, CAO Y. Study on fuzzy variable structure tracking of airborne laser communication terminals [J]. Semiconductor Optoelectronics, 2015, 36(1):125-127.

- 率自适应无线光通信机的研制[J]. 西安理工大学学报, 2014, 30(4):443-447.

WU P F, KE X ZH, YUAN Q. Research and development of a 10 Mbit/s ~ 1 Gbit/s rate adaptive optical wireless communication machine [J]. Journal of Xi'an University of Technology, 2014, 30(4):443-447.

吴鹏飞, 柯熙政, 袁泉. 一种 10 Mbit/s~1 Gbit/s 速

- [8] 徐海军,刘金刚,王益华. 基于 ARM 核的嵌入式 TCP/IP 协议栈简化实现[J]. 计算机应用研究, 2006, 23(10):251-253.

XU H J, LIU J G, WANG Y H. Simplified realization of embedded TCP/IP protocol stack based on ARM core[J]. Application Research of Computers, 2006, 23(10):251-253.

- [9] 刘黎明,王用玺. 基于 NicheStack TCP/IP 协议栈的嵌入式以太网控制器的设计与实现[J]. 郑州轻工业学院学报:自然科学版, 2015, 30(1):95-97.

LIU L M, WANG Y X. Design and realization of the

- embedded ethernet controller based on NicheStack TCP/IP protocol stack[J]. Journal of Zhengzhou University of Light Industry: Natural Science Edition, 2015, 30(1): 95-97.

- [10] 刘国营,马力. 基于数据链路层的网络透明传输[J]. 现代电子技术. 2004,27 (16): 183-186.

LIU G Y, MA L. The transparent transmission based on the datalink layer[J]. Modern Electronics Technique, 2004, 27 (16): 183-186.

- [11] CHAURE R, PANDE N A. Design and implementation of ethernet based embedded network controller using ARM 7(LPC2148) processor [C]. World Conference on Futuristic Trends in Research and Innovation for Social Welfare (Startup Conclave), Coimbatore, 2016: 1-4.

- [12] 胡青. 基于 UC/OS II 与 Nios II 的以太网接口软件设计[J]. 声学与电子工程,2013(2):33—36.

HU Q. Software design of an ethernet interface based on μC/OS-II and nios II [J] Acoustics and Electronics Engineering, 2013(2):33-36.

- [13] 左震, 邓黠, 唐贵林,等. 基于 Nios 软核处理器的以太网接口设计[J]. 计算机测量与控制, 2009, 17(4):763-766.

ZUO ZH, DENG J, TANG G L, et al. Design of an ethernet interface based on the nios soft-core processor[J]. Computer Measurement & Control, 2009, 17(4):763-766.

- [14] 郑云龙. 基于 Nios II 的以太网控制器的设计[D]. 哈尔滨:哈尔滨工业大学, 2009.

ZHENG Y L. The design of ethernet controller basis on nios II [D]. Harbin: Harbin Institute of Technology, 2009.

- [15] KHALILZAD N M, YEKEH F, ASPLUND L, et al. FPGA implementation of real-time Ethernet communication using RMII interface [C]. IEEE 3rd International Conference on Communication Software and Networks, 2011;35-39.

- [16] 孙科达,石旭刚,史故臣. 一种新的 8B/10B 编解码方案设计与实现[J]. 光传输,2009(7):27-30.

SUN K D, SHI X G, SHI G CH. A new method of design and implementation on 8B/10B encoding and decoding[J]. Optical Communication Technology, 2009(7):27-30.

- [17] 李宥谋. 8B/10B 编码器的设计及实现[J]. 电讯技术. 2005 (6):28-32.

LI Y M. Design and realization of an 8B/10B

encoder[J]. Telecommunication Engineering, 2005(6):

28-32.

- [18] 王飞. 基于 FPGA 的全数字化峰值时刻检测技术[J]. 电子测量与仪器学报, 2015, 29(6):914-919. WANG F. Full digital peak time discrimination technique based on FPGA[J]. Journal of Electronic Measurement and Instrumentation, 2015, 29(6):914-919.

- [19] 于志翔. 光发射模块温度补偿系统的设计与实现[J]. 电子测量技术, 2016,39(9):145-148,181.

YU ZH X. Design and implementation of temperature compensation system for optical transceiver module[J].

Electronic Measurement Technology, 2016,39(9):145-148,181.

#### 作者简介

**亢烨**,2005 年于南京邮电大学获得学 士学位,2013 年于西安理工大学获得硕士 学位,现为西安理工大学电路与系统专业博 士在读,主要研究方向为光通信。

E-mail: kangye@ stu. xaut. edu. cn

Kang Ye received his B. Sc. degree in 2005 from Nanjing university of Posts and Telecommunications, received his M. Sc. degree in 2013 from Xi' an university of Technology. Now he is a Ph. D. Candidate in circuits and system at Xi' an university of Technology. His main research interest includes Optical communication.