· 85 ·

DOI: 10. 13382/j. jemi. B2003056

# 基于 C 单元的抗干扰低功耗双边沿触发器\*

黄正峰<sup>1</sup> 杨 潇<sup>1</sup> 国欣祯<sup>1</sup> 咸昊琛<sup>1</sup> 鲁迎春<sup>1</sup> 欧阳一鸣<sup>2</sup> 倪天明<sup>3</sup> 徐 奇<sup>1</sup> (1. 合肥工业大学 电子科学与应用物理学院 合肥 230601; 2. 合肥工业大学 计算机与信息学院 合肥 230601; 3. 安徽工程大学 电气工程学院 芜湖 241000)

摘 要:快速增长的功耗是 VLSI 设计中的重要问题,特别是输入信号中存在毛刺,双边沿触发器的功耗将会显著增大。为了有效降低功耗,提出了一种基于 C 单元的抗干扰低功耗双边沿触发器 AILP-DET,结构采用快速的 C 单元,不仅能够阻塞输入信号存在的毛刺,阻止触发器内部冗余跳变的发生,降低晶体管的充放电频率;而且增加了上拉-下拉路径,降低了其延迟。相比现有的双边沿触发器,AILP-DET 只在时钟边沿采样,有效降低了功耗。通过 HSPICE 仿真,与 10 种双边沿触发器相比较, AILP-DET 仅仅增加了 7.58%的延迟开销,无输入毛刺情况下总功耗平均降低了 261.28%,有输入毛刺情况下总功耗平均降低了 46.97%。详尽的电压温度波动分析表明,该双边沿触发器对电压、温度等波动不敏感。

关键词:双边沿触发器:毛刺:低功耗:C单元:时钟树

中图分类号: TN432 文献标识码: A 国家标准学科分类代码: 510.3040

# Anti-interference low-power double edge-triggered flip-flop based on C-elements

Huang Zhengfeng<sup>1</sup> Yang Xiao<sup>1</sup> Guo Xinzhen<sup>1</sup> Qi Haochen<sup>1</sup> Lu Yingchun<sup>1</sup>

Ouyang Yiming<sup>2</sup> Ni Tianming<sup>3</sup> Xu Qi<sup>1</sup>

- (1. School of Electronic Science & Applied Physics, Hefei University of Technology, Hefei 230601, China;

- 2. School of Computer & Information, Hefei University of Technology, Hefei 230601, China;

- 3. School of Electrical Engineering, Anhui Polytechnic University, Wuhu 241000, China)

Abstract: One of the paramount issues in the field of VLSI design is the rapid increase in power consumption. When the input signal is interfered and glitches occur, the power consumption of the double edge-triggered flip-flop (DETFF) will increase significantly. In order to effectively reduce the power consumption, this paper proposed an anti-interference low-power double edge-triggered flip-flop based on C-elements. The improved C-element is used in this DETFF. One side, it effectively blocks the glitches in the input signal, prevents redundant transitions inside the DETFF, and reduces the charge and discharge frequency of the transistor. The C-element also adds pull-up and pull-down paths, reducing its latency. Compared with other existing DETFFS, the DETFF proposed in this paper only flips once on the clock edge, which effectively reduces power consumption. The HSPICE is used to simulate the proposed DETFF and the other 10 DETFFs, AILP-DET only increased the delay overhead by 7.58%, the total power consumption is reduced by an average of 261.28% without input glitches, and the average power consumption is reduced by 46.97% with input glitches. Detailed voltage and temperature variations analysis indicate that the proposed DETFF features are less sensitive to voltage and temperature variations.

Keywords: double edge-triggered flip-flop; glitch; lower power; C-element; clock tree circuit

# 0 引 言

集成电路产业技术的不断进步,带来了其规模持续性扩大,一方面日益先进的制程将集成电路工艺带入到深亚微米阶段,另一方面越来越高的集成度使晶体管数目成倍的增加,这些变化都导致集成电路功耗问题日益显著<sup>[1]</sup>。近年来,便携式消费类电子设备的迅速增加和电路工作时钟频率的提高增加了电路设计中降低功耗的必要性<sup>[2]</sup>。因此,低功耗问题已经成为现代集成电路设计中关键的挑战之一。

对于数字集成电路来说,其时序电路的功耗在整个电路总功耗中占了相当大的比重。在时序电路中,时钟系统主要由时钟树电路与时序单元组成,花费在时钟树和时序单元上的功耗是总功耗的主要来源。触发器作为集成电路中的时序元件,广泛应用于有限状态机控制器、流水线电路或存储元件中,其功耗可以占到电路总功耗的20%~45%。作为一种基本元件而设计的低功耗触发器能够为降低集成电路总功耗提供巨大的优势<sup>[3-5]</sup>。时钟树电路为整个时序电路提供时钟信号,所以它的输出负载比较大,导致其晶体管尺寸相对较大,从而带来更大的功耗,通常能够占到电路总功耗的40%左右,需要进行有效控制<sup>[6-8]</sup>。

根据触发工作方式的差别,触发器可以分成单边沿触发器(SETFF)和双边沿触发器(DETFF)。SETFF 仅仅在上升沿或者下降沿进行数据采样,DETFF则同时在上升沿和下降沿进行数据采样。在给定相同的时钟频率下,DETFF的数据吞吐量是 SETFF 的 2 倍[9-11]。现有的DETFF 设计主要分为数据选择器型、脉冲型、C 单元型和真单向时钟型 4 类。数据选择器型 DETFF 存在时钟信号引起的较高功耗;脉冲型 DETFF 驱动电流较小,因此会带来较高的数据传输延迟;传统 C 单元型触发器对于晶体管尺寸要求严苛,不利于低功耗设计;真单向时钟型触发器由于使用单向时钟,降低了时钟树功耗,但是却大大增加了面积开销。

降低时钟信号的翻转频率,减小时钟负载电容等方案,可以有效地降低时钟功耗。本文使用了时钟门控技术,当触发器输入端信号保持不变时,暂时关断对应的晶体管,减少其动态功耗。另一方面,本文使用了快速的 C单元,能够阻塞由于各方面干扰而产生的输入信号上的毛刺。当输入上存在毛刺并传到触发器内部时,存在产生内部节点的冗余跳变的可能,造成额外的功耗开销。

CMOS 电路功耗主要来源于动态功耗和静态功耗。 动态功耗产生来自于电路节点的频繁充放电,可以通过 式(1)建模[11]。

$$P_d = \alpha \cdot C_L \cdot V_{dd}^2 \cdot f_{\text{clk}} \tag{1}$$

式中: $P_d$  为动态功耗, $\alpha$  为开关活动性, $C_L$  为节点电容, $V_{dd}$  为电源电压, $f_{clk}$  为时钟频率。同时,在数字电路信号传播过程中,一般会伴随着因为各种干扰产生各种毛刺。虽然毛刺对电路的功能的影响可能会较小甚至没有,但是会引起大量的冗余跳变产生额外功耗。阻塞由于信号干扰产生的毛刺可以是有效降低电路功耗的方法之一。

#### 1 四种类型的双边沿触发器

#### 1.1 数据选择器型双边沿触发器

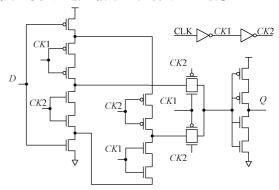

文献[12]提出了使用堆叠技术的数据选择器型双边沿触发器 TCRFF,如图 1 所示,包括一个数据选择器、由两个反相器组成的时钟树和两个堆叠 MOS 管的锁存器,并且复用了输入信号 D 控制的 MOS 管。

图 1 TCRFF 双边沿触发器

Fig. 1 Double edge-triggered flip-flop TCRFF

TCRFF 在两个锁存器的时钟信号输入端都使用了堆叠技术,减少了其泄漏电流。当输入 D=0 时,若 CLK 为高电平,则 CK1=0, CK2=1,此时 P1、P2、P3 导通,当 CLK 边沿到来, CLK 变为低电平,则 CK1=1, CK2=0,此时 P1、P4、P5 导通,当时钟信号 CLK 切换时,数据选择器再选通处于保持状态的值进行输出。同时,输出级的反相器部分,TCRFF 也使用了堆叠技术,当多个 MOS 晶体管被配置成串联,其中一个或多个晶体管被关断时,应用该方法可以有效减少泄漏电流。

TCRFF的缺点同样来自于 MOS 管堆叠技术的使用。相比于不堆叠的晶体管,使用堆叠技术的 MOS 管的驱动电流会小很多,导致更高的传播延迟<sup>[13]</sup>。

#### 1.2 C 单元型双边沿触发器

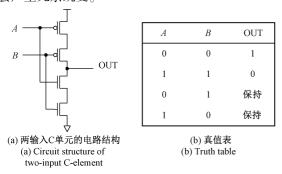

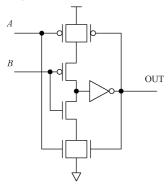

文献[14]提到的 C 单元,一般为双输入单输出的三端器件。当双输入相同时,输出将变为输入值。当输入不相同时,保留上一状态的输出值。该器件可以充当一个锁存器,通过输入端信号电平的适当组合进行设置和重置。

C单元能够阻塞毛刺的传播,其电路结构与其真值表如图 2 所示。当 C单元的两个输入相同时,其功能和反相器相当,对输入信号取反并进行输出;当 C单元的两个输入不相同时,其输出保持不变。由真值表可知,如果 C单元中的一路数据输入存在毛刺,另外一路数据输入正确的时候,不会改变 C单元的输出[14],下一级的电路不会产生冗余跳变。

图 2 两输入 C 单元的电路结构与真值表 Fig. 2 Circuit structure of two-input C-element and its truth table

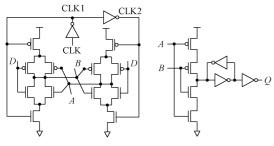

图 3 所示为文献[14]提出的双边沿触发器 IP\_C。IP\_C 同样由锁存器 A 和 B、输出 C 单元组成。IP\_C 的内部锁存器 A 和 B 分别由两个 C 单元组成,精简了之前的保持器,而输出 C 单元同样由 C 单元和保持器组成。由于 IP\_C 也是由 C 单元构成,同样阻止了冗余跳变的产生。IP\_C 减少了由于时钟信号转换时而产生的动态功耗,其工作原理如下。IP\_C 在节点 A 和 B 处没有静态存储锁存器,输入 C 单元实质上是 CLK1 和 CLK2 信号的反相器。当 CLK 信号改变时,输入 C 单元将 A 或 B 的状态切换,再通过内部连接的 C 单元改变 B 或 A 的状态,当 A 和 B 的状态相同都为输入信号 D 时,再通过输出 C 单元进行输出。因为 IP\_C 是在每个时钟边沿处一个很小的 A 和 B 状态相同的时间窗口进行输出,该设计是属于隐式脉冲型双边沿触发器。

图 3 IP\_C 双边沿触发器

Fig. 3 Double edge-triggered flip-flop IP\_C

$IP_{-}C$  的缺点在于,无论 D 和 Q 的状态如何,A 和 B 的电平在每个时钟跳变后都会改变,从而产生由于时钟

信号切换引起的高功耗。

#### 1.3 脉冲型双边沿触发器

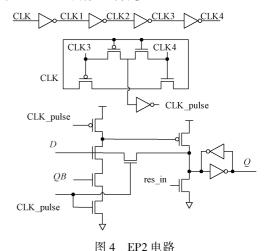

文献[15]提出的脉冲式双边沿触发器 EP2 如图 4 所示,包括 4 个反相器组成的时钟树,6 个晶体管组成的脉冲发生器以及锁存器部分。

Fig. 4 Circuit structure of EP2

EP2 通过对时钟信号 CLK 进行延迟操作,再通过脉冲发生器产生采样脉冲,使锁存器在每个时钟边沿进行采样,实现双边沿触发的功能。EP2 为了实现采样脉冲,对于脉冲发生器的晶体管尺寸要求比较苛刻,两个PMOS 管的尺寸要远大于两个 NMOS 管的尺寸,这也给降低电路的功耗带来了不利的影响。

#### 1.4 真单相时钟型双边沿触发器

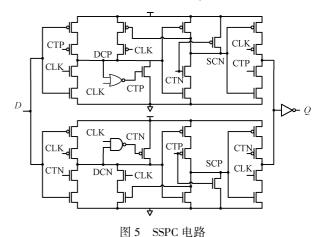

图 5 所示为文献[16]提出的真单相时钟型双边沿触发器 SSPC。SSPC 只使用单相时钟 CLK,不使用其反相信号,因此也不需要额外的反相器组成的时钟树电路,可以大幅度地降低时钟树上所消耗的功耗。同时,真单相时钟的使用也降低了 SSPC 的延迟。

Fig. 5 Circuit structure of SSPC

但是 SSPC 的缺点同样明显。为了减少反相时钟的使用,SSPC 使用了大量的晶体管,带来了巨大的面积开销。另一方面,真单相时钟技术增大了 SSPC 的保持时间和最小锁存窗口时间。

### 2 本文提出的双边沿触发器

#### 2.1 电路结构

首先,对传统的 C 单元进行拓展,得到本文结构所使用的快速的 C 单元,如图 6 所示。增加了 C 单元的反馈回路,保持其静态特性。另外,也使 C 单元的上拉和下拉能力得到了提升,显著增快了其传输速度<sup>[17]</sup>。

图 6 快速的 C 单元

Fig. 6 Fast C-element

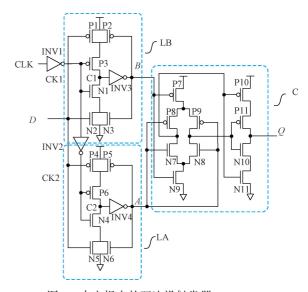

分析已有的双边沿触发器特点,本文提出了基于 C 单元的抗干扰低功耗双边沿触发器 AILP-DET,其晶体管级电路如图 7 所示。该双边沿触发器包括由反相器 INV1 和 INV2 组成的时钟树,两个使用快速的 C 单元组成的内部锁存器 A 和 B,以及 3 个 C 单元组成的输出级。时钟树电路产生时钟信号以及时钟的反相信号。内部锁存器 A 和 B 分别在时钟高低电平时锁存输入 D 的值。输出级将内部锁存器锁存的 D 的值输出到 Q,同时,3 个 C 单元和 MOS 管堆叠的使用保证了该双边沿触发器能够在低频下工作,最低工作时钟频率可以到达 5 MHz。

#### 2.2 工作原理

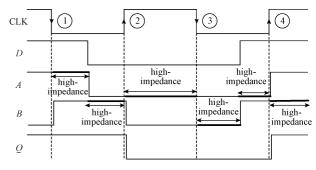

图 8 所示为本文结构的工作原理,在时钟边沿到来之前,任何 D 的变化都不会影响输出 Q,只有边沿到来时才会采样 D 的值。在时钟的的第 1 个下降沿和上升沿之间,D 改变之前 A 保持在高阻态,逻辑状态为之前的 1,B 处于状态 1,此时输出 Q 为 1;当 D 产生翻转,A 翻转到逻辑 0,B 处于高阻态,逻辑值为 1,经由 C 单元输出 Q 依然为 1。在第 2 个下降沿之前,D 和 B 的逻辑值都为 0,A 处于高阻态,状态是之前的 0,此时输出 Q 为 0;当第 2 个时钟下降沿到来,D 仍处于逻辑值 0,这时 A 的逻辑值为 1,

图 7 本文提出的双边沿触发器 AILP-DET

Fig. 7 Proposed double edge-triggered flip-flop AILP-DET

B 保持着高阻态,所以输出 Q 依然为 0。只有当时钟边沿到来且 Q 与 D 不同时,输出 Q 才会翻转到 D。

锁存器 A 和 B 作为整个电路的输入端,其节点逻辑值在时钟不同的电平期间和输入 D 相同,而不和 D 相同的节点会处于保持态,时钟边沿到来时,不和 D 相同的节点逻辑值就会切换到 D,这时 A 和 B 的逻辑值相同,且都为 D,使输出 Q 切换为输入 D,完成双边沿触发的功能。其中,保持原逻辑值是因为采用了快速的 C 单元,锁存器 A 或者 B 有较好的静态特性。另一方面,因为内部节点冗余跳变减少,会降低整体电路功耗。

图 8 工作原理波形

Fig. 8 Working principle waveform

节点 A、B 和输出 Q 的工作真值表如表 1 所示,其中保持不变表示 Q 保持上一周期输出,高阻态则说明锁存器处于保持状态。由先前介绍的 C 单元功能可知,其输出不会受到输入中存在的高阻态的影响,只会处于保持状态。只有当内部节点 A 和 B 的逻辑值相同时,双边沿触发器的输出 Q 才和输入 D 相同。

表 1 节点  $A \setminus B$  和 Q 的状态真值表

| Table 1 | Truth | table | of n | ode . | <b>A</b> . | R | and | 0 |

|---------|-------|-------|------|-------|------------|---|-----|---|

| A   | В   | Q    |

|-----|-----|------|

| 0   | 0   | 0    |

| 0   | 1   | 保持不变 |

| 1   | 0   | 保持不变 |

| 1   | 1   | 1    |

| 高阻态 | 1   | 保持不变 |

| 高阻态 | 0   | 保持不变 |

| 1   | 高阻态 | 保持不变 |

| 0   | 高阻态 | 保持不变 |

#### 2.3 仿真结果

本文基于 HSPICE 平台对提出的 AILP-DET 进行了 仿真。采用 32 nm PTM 工艺,电源电压为 0.9 V,温度为 25 °C,时钟频率为 250 MHz,时钟周期为 4 ns。

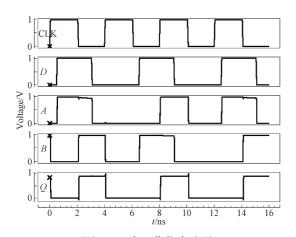

图 9 所示为使用 HSPICE 仿真得到的波形。在图 9 中,CLK 为时钟信号,D 和 Q 分别为输入和输出信号,A 和 B 分别为节点 A 和 B 的逻辑值。从仿真波形图中可以看到,AILP-DET 在时钟的上升沿和下降沿均成功采样到输入信号 D 的值并传播到输出信号 Q,实现了双边沿触发的功能。

图 9 正常工作仿真波形

Fig. 9 Normal working simulation waveform

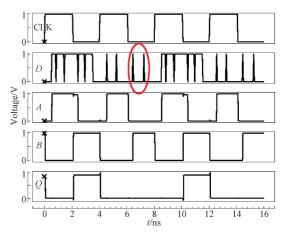

图 10 所示为遭受干扰在输入信号 D 上产生大量毛刺时的仿真波形。图 10 中,仿真条件和时钟信号 CLK 与上文一致,同时,设置在每个时钟周期内,输入信号 D 上存在 4 个毛刺。A 和 B 分别为锁存器 A 和 B 的值,Q 为输出信号。从仿真图可以看出,在时钟边沿之间,锁存器 A 或 B 的输出状态只会翻转一次或者不翻转保持着原来的逻辑值。所以,当输入信号有毛刺存在时,对锁存器 A 和 B 基本不会产生影响。

说明本文提出的 AILP-DET 能够阻塞干扰产生的毛刺,不会使其直接传输到两个内部节点,也就不会带来冗

余跳变,降低了电路内部节点翻转概率,晶体管充放电的频率降低,带来了电路功耗的缩减。

图 10 存在毛刺仿真波形

Fig. 10 Working simulation waveform with glitches

# 3 实验结果与比较分析

本文基于 32 nm PTM 工艺对本文结构以及相应的双边沿触发器进行了 HSPICE 仿真,得到的数据结果如表 2 所示,其中电源电压 VDD=0.9 V,时钟频率 CLK=250 MHz,温度为 25  $^{\circ}$ C。

表 2 中,# of T 表示晶体管数,TP 表示电路总功耗, $t_{cq}$  表示时钟信号 CLK 到输出信号 Q 的延迟,PDP 表示电路的功耗延迟积,是一个重要的复合指标, $t_{setup}$  表示触发器的建立时间, $t_{hold}$  表示触发器的保持时间,CTP 表示电路的时钟树功耗, $P_{glitch}$  表示在一个时钟周期中有两个毛刺情况下的电路总功耗。

从表 2 可知, LM2<sup>[18]</sup>、EP1<sup>[19]</sup>和 EP2 的电路总功耗相对较大。LM2 使用传输管代替传输门和反相器,而且部分晶体管的源极直接由时钟信号控制,造成较大的功耗问题,同时,LM2 存在的电平冲突问题也是造成其功耗过大的原因之一。而 EP1 和 EP2 都是显式脉冲型双边沿触发器,其脉冲发生器部分会产生较大的功耗开销,造成其电路总功耗比较大。同时可以看到,本文提出的 AILP-DET 电路总功耗在 11 种触发器中是最低的。

在电路延迟方面,LMI 和 SSPC 的延迟是最小的两个,而 LG\_C<sup>[20]</sup>和 IP\_C 等使用了 C 单元的双边沿触发器的延迟较大,这是因为其设计都采用了 C 单元,其驱动电流较小,造成了过高的延迟。本文提出的 AILP-DET 也采用了 C 单元进行设计,但是和 LG\_C 和 IP\_C 等相比要低得多,这是因为其采用了快速的 C 单元,额外增加的晶体管也提升了其上拉和下拉能力,带来了更低的延迟。

| 表 2 本文提出的 AILP-DET 与其他 DETFF 的性能比较 |

|------------------------------------|

|                                    |

| Table 2 T | The nerformance | comparison | of AH P-DET | proposed in this par | per with other DETFFs |

|-----------|-----------------|------------|-------------|----------------------|-----------------------|

| DETFF | # of T | TP/μW  | $t_{ m eq}/{ m ps}$ | PDP/aJ  | $t_{ m setup}/{ m ps}$ | $t_{ m hold}/{ m ps}$ | CTP/μW | $P_{ m glitch}/\mu{ m W}$ |

|-------|--------|--------|---------------------|---------|------------------------|-----------------------|--------|---------------------------|

| LM1   | 26     | 1.75   | 37. 14              | 65. 18  | 13. 20                 | 28. 39                | 1. 14  | 2. 22                     |

| LM2   | 22     | 23. 80 | 39. 34              | 936. 07 | 11. 22                 | 57. 32                | 22. 51 | 21.60                     |

| TCRFF | 22     | 1. 52  | 80. 97              | 123. 34 | 54. 22                 | 45. 52                | 0.81   | 2. 11                     |

| LM_C  | 26     | 1. 22  | 72. 20              | 88. 11  | 36. 50                 | 66. 84                | 0. 23  | 1.59                      |

| LG_C  | 28     | 1.44   | 84. 04              | 120. 66 | 16. 11                 | 167. 00               | 0. 26  | 1.85                      |

| IP_C  | 26     | 1. 39  | 77. 65              | 107. 65 | -25.08                 | 148. 59               | 0. 29  | 1. 39                     |

| FN_C  | 30     | 1. 18  | 74. 28              | 87. 28  | 15. 59                 | 101. 43               | 0. 32  | 1.36                      |

| EP1   | 22     | 2. 29  | 51.42               | 117. 65 | -2.42                  | 61. 69                | 1.90   | 2. 25                     |

| EP2   | 25     | 3. 35  | 46. 42              | 155. 59 | -18. 11                | 56. 42                | 3. 16  | 3.34                      |

| SSPC  | 40     | 1. 21  | 37. 28              | 45. 28  | 30. 39                 | 292. 58               | 0. 27  | 1.65                      |

| 本文    | 30     | 0. 98  | 58. 28              | 56. 92  | 5. 62                  | 62. 56                | 0. 26  | 1.07                      |

平均

在电路的功耗延迟积(power delay product,PDP)方面,SSPC 的 PDP 最低,LM2 的 PDP 最大,AILP-DET 的 PDP 的次低。但是 SSPC 所使用的晶体管数目比本文提出的触发器高出了 33.3%,所以 AILP-DET 有着比较好的综合性能。

LM2由于过大的时钟负载,以及之前提到的源极与时钟直连的问题,导致时钟树功耗偏大;在 EP1和 EP2中,开销过大的脉冲发生器也带来了过大的时钟树功耗。而本文提出的 AILP-DET 因为 C 单元的使用,使得时钟树功耗降低,可以看到其时钟树功耗是处于次优的。

当输入中受到干扰产生毛刺时,LM1产生的波动较大,其电路总功耗会显著增加。因为毛刺会带来内部锁存器的逻辑值随之翻转,带来冗余跳变增加动态功耗。LG\_C 因为 C 单元的使用,通过其功能阻止毛刺传入电路内部,使其影响降低,但是 LG\_C 的 3 个保持器,无论输入信号是否有毛刺,都始终在工作状态,带来了较大动态功耗。而由于 AILP-DET 采用了快速的 C 单元,同样使电路中的冗余跳变减少,降低电路总功耗。由表 2 可知,在存在毛刺的情况下其功耗是最小的。

表 3 为本文提出的 AILP-DET 与相关结构的相对总功耗开销  $\Delta TP$ 、相对延迟开销  $\Delta t_{eq}$  和相对 PDP 开销  $\Delta PDP$ ,其中  $\Delta = 100\% \times (($  对比双边沿触发器 -本文提出 双边沿触发器)/对比双边沿触发器)。若  $\Delta$  为正,则意味着该项指标 AILP-DET 优于对比结构;若  $\Delta$  为负,则意味着该项指标 AILP-DET 劣于对比结构。从表 3 可以看到,本文提出的触发器在电路总功耗方面,优于所有的对比双边沿触发器,平均节省 261. 28%的电路总功耗,同时,也平均提升了 41. 99%的 PDP,只增加了 7. 58%的延迟。

使用同样的方法来对比相关双边沿触发器在受到干扰输入信号上产生毛刺时的电路总功耗。对比了一个时钟周期中存在两个毛刺情况下的相对电路总功耗  $\Delta P_{\text{elith}}$ ,其中  $\Delta$  以及对比方法和上文介绍的相同。对比

表 3 相对开销比较

Table 3 Relative cost comparison (%)

-7.58

41.99

$\Delta t_{\rm eq}$  $\Delta PDP$ DETFF  $\Delta TP$ LM1 44.34 -56.89 12.68 LM2 2 282.03 -48.1593.92 **TCRFF** 35.88 28.03 53.85  $LM_C$ 24.36 19.29 35.40  $LG_C$ 31.97 30.66 52.83 IP\_C 24.95 47.13 29.55 FN\_C 21.55 34.79 16.88 EP1 57.31 -13.3351.62 EP2 70.86 -25.5463.42 SSPC 19.59 -56.34-25.71

结果如表 4 所示,可以看到,本文提出的 AILP-DET 在输入信号存在毛刺的情况下的电路总功耗优于所有的对比触发器,平均提升了 46.97%。

261.28

表 4 受到干扰产生毛刺相对开销比较

Table 4 Relative cost comparison with glitches

| DETFF | $\Delta P_{ m glitch}/\%$ |

|-------|---------------------------|

| LM1   | 51. 76                    |

| LM2   | 95. 04                    |

| TCRFF | 49. 08                    |

| LM_C  | 32. 50                    |

| LG_C  | 42. 11                    |

| IP_C  | 22. 83                    |

| FN_C  | 21. 43                    |

| EP1   | 52. 25                    |

| EP2   | 67. 90                    |

| SSPC  | 34. 83                    |

| 平均    | 46. 97                    |

综上所述,与相关的边沿触发器进行比较,本文提出的双边沿触发器 AILP-DET 在总功耗、延迟、PDP 和存在毛刺时的总功耗等方面取得了较大的优势。

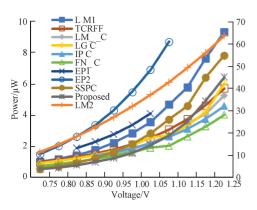

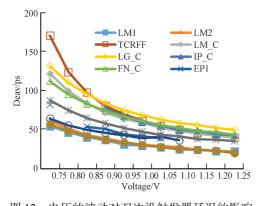

# 4 电压与温度波动分析

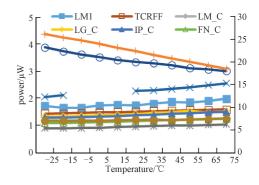

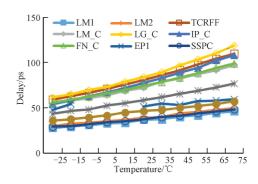

随着集成电路技术的不停发展,工艺不停进步,电压与温度波动对于纳米尺度下的集成电路可靠性具有越来越严重的影响[17]。评估了双边沿触发器在电压和温度波动下的功耗和延迟性能。如图 11 和 12 所示,电压由 0.75 增加到 1.25 V,步长为 0.05 V。由于 LM2 功耗相对其他的双边沿触发器较大,其使用图中右侧的次坐标轴。从图 11 可以看出,电路的功耗随着电压的增长而增长。图 12 中,电路延迟随着电压的增长而不断降低,这是因为供电电压越大,导通电流的速度就越快,则延迟越小。

另一方面,可以看到 IP\_C 在 0.75、0.8 和 0.85 V 等低电压时不能正常工作,而 EP1 和 EP2 在 1.15、1.2 和 1.25 V 等高电压时不能正常工作,它们对于电压的波动很敏感。而本文提出的 AILP-DET 则在 0.75~1.25 V 的电压波动下都可以正常工作,对电压波动不敏感。

图 11 电压的波动对双边沿触发器功耗的影响 Fig. 11 Influence of voltage variation on power consumption of DETFFs

图 12 电压的波动对双边沿触发器延迟的影响 Fig. 12 Influence of voltage variation on delay of DETFFs

温度波动对于双边沿触发器的性能影响如图 13 和 14 所示,其中温度从-25 %-75 %,步长为 10 %。需要注意的是,由于 LM2 功耗相对其他的双边沿触发器较大,其使用图中右侧的次坐标轴。从图 13、14 可以看到,双边沿触发器的功耗与延迟都因为温度的升高而升高。温度的升高会导致晶体管载流子迁移率下降,使其功耗和延迟升高。

图 13 温度的波动对双边沿触发器功耗的影响 Fig. 13 Influence of temperature variation on power consumption of DETFFs

图 14 温度的波动对双边沿触发器延迟的影响 Fig. 14 Influence of temperature variation on delay of DETFFs

表 5 和 6 提供了与上图实验数据相应的方差数据,同样可以验证本文结构的稳定性。

# 5 结 论

为了有效降低双边沿触发器的功耗,本文提出了基于 C 单元的抗干扰低功耗双边沿触发器 AILP-DET。使用快速的 C 单元,使电路时钟负载降低,带来了较低的时

表 5 电压波动功耗延迟方差比较

Table 5 Voltage variation power consumption delay variance comparison

| 功耗方差     | 延迟方差                                                                                               |

|----------|----------------------------------------------------------------------------------------------------|

| 7. 762   | 112. 386                                                                                           |

| 297. 840 | 156. 512                                                                                           |

| 2. 366   | 1624. 472                                                                                          |

| 2. 186   | 680. 241                                                                                           |

| 2. 428   | 686. 438                                                                                           |

| 1. 229   | 141. 672 3                                                                                         |

| 1. 096   | 477. 085                                                                                           |

| 0. 973   | 237. 406                                                                                           |

| 6. 301   | 85. 526                                                                                            |

| 5. 895   | 132. 008                                                                                           |

| 3. 722   | 284. 053                                                                                           |

|          | 7. 762<br>297. 840<br>2. 366<br>2. 186<br>2. 428<br>1. 229<br>1. 096<br>0. 973<br>6. 301<br>5. 895 |

表 6 温度波动功耗延迟方差比较

Table 6 Temperature variation power consumption delay variance comparison

|       | -      |          |

|-------|--------|----------|

| DETFF | 功耗方差   | 延迟方差     |

| LM1   | 0. 011 | 37. 333  |

| LM2   | 6.610  | 44. 425  |

| TCRFF | 0.003  | 292. 999 |

| LM_C  | 0.001  | 210. 989 |

| LG_C  | 0.006  | 363. 001 |

| IP_C  | 0.006  | 319. 152 |

| FN_C  | 0.003  | 209. 741 |

| EP1   | 0.029  | 14. 453  |

| EP2   | 0.079  | 48. 781  |

| SSPC  | 0.001  | 42. 864  |

| 本文    | 0.003  | 122. 494 |

钟树功耗。同时,也有效减少了电路内部节点的冗余跳变,进一步降低了电路的整体功耗。与相关双边沿触发器相比,本文提出的结构在总功耗、时钟树功耗、PDP以及抗干扰减少毛刺影响方面都具有很大的优势,具有比较好的综合性能。电压与温度波动分析表明其对于电压、温度等波动不敏感,具有较高的可靠性。

#### 参考文献

37(12):71-75.

- [ 1 ] KEATING M, FLYNN D, AITKEN R, et al. Low power methodology manual: For system-on-chip design [ M ]. Newyork: Springer, 2007.

- [2] 张宏达,王黎明,赵英亮,等. 一种改进的数字 Costas 环及 FPGA 实现[J]. 国外电子测量技术, 2018, 37(12):71-75.

ZHANG H D, WANG L M, ZHAO Y L, et al. Improved digital Costas loop and FPGA implementation [J].

Foreign Electronic Measurement Technology, 2018,

- [3] 欧阳一鸣, 胡立柱, 安鑫, 等. 无线片上网络高性能 EMS 容错方案设计[J]. 仪器仪表学报, 2018, 39(5): 132-140.

- OUYANG Y M, HU L ZH, AN X, et al. High performance EMS fault tolerant scheme for wireless network on chip [J]. Chinese Journal of Scientific Instrument, 2018, 39(5):132-140.

- [4] 张阿敏, 王春华, 杜高明, 等. 兼顾热优化的 TSV 容错设计 [J]. 电子测量与仪器学报, 2018, 32(7): 180-186.

ZHANG A M, WANG CH H, DU G M, et al. TSV redundancy strategy considering thermal optimization [J]. Journal of Electronic Measurement and Instrumentation, 2018, 32(7):180-186.

- [5] 刘颖,王敏,文渊,等. 低功耗刷卡器的设计[J]. 电子测量技术,2017,40(11):197-200.

LIU Y, WANG M, WEN Y, et al. Design of low power card reader [J]. Electronic Measurement Technology, 2017,40(11):197-200.

- [6] DAI Y, SHEN J. An explicit-pulsed double-edge triggered JK flip-flop[C]. 2009 International Conference on Wireless Communications & Signal Processing, IEEE, 2009: 1-4.

- [7] ZHAO P, MCNEELY J, GOLCONDA P, et al. Low-power clock branch sharing double-edge triggered flip-flop [J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2007, 15(3): 338-345.

- [8] YU C C. Low-power double edge-triggered flip-flop circuit design[C]. 2008 3rd International Conference on Innovative Computing Information and Control, IEEE, 2008; 566-566.

- [ 9 ] NEDOVIC N, OKLOBDZIJA V G. Dual-edge triggered storage elements and clocking strategy for low-power systems [ J ]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2005, 13(5): 577-590.

- [10] TIWARI S C, SINGH K, GUPTA M. A low power high density double edge triggered flip flop for low voltage systems [C]. 2010 International Conference on Advances in Recent Technologies in Communication and Computing, IEEE, 2010; 377-380.

- [11] LEE Y, SHIN G, LEE Y. A fully static true-single-phase-clocked dual-edge-triggered flip-flop for near-threshold voltage operation in IoT applications[J]. IEEE Access, 2020(8): 40232-40245.

- [12] LAPSHEV S, HASAN S M R. New low glitch and low power DET flip-flops using multiple C-elements [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2016, 63(10): 1673-1681.

- [13] SABU A N, BATRI K. Design and analysis of power efficient TG based dual edge triggered flip-flops with stacking technique[J]. Journal of Circuits, Systems and Computers, 2020, 29(8): 37.

- [14] TSCHANZ J, NARENDRA S, CHEN Z, et al. Comparative delay and energy of single edge-triggered & dual edge-triggered pulsed flip-flops for high-performance microprocessors [ C ]. Proceedings of the 2001 International Symposium on Low Power Electronics and Design, 2001; 147-152.

- [15] LEE Y, LEE Y. A PVT variation-tolerant static singlephase clocked dual-edge triggered flip-flop for aggressive voltage scaling [J]. IEICE Electronics Express, 2019, 16(20): 20190528-20190528.

- [16] WEY I C, WU B C, PENG C C, et al. Robust C-element design for soft-error mitigation [J]. IEICE Electronics Express, 2015, 12(10): 20150268-20150268.

- [17] ZHANG Y, KHAYATZADEH M, YANG K, et al. Irazor: Current-based error detection and correction scheme for PVT variation in 40-nm arm cortex-r4 processor [J]. IEEE Journal of Solid-State Circuits, 2017, 53(2): 619-631.

- [18] KHAN I A, SHAIKH D, BEG M T. 2 GHz low power double edge triggered flip-flop in 65nm CMOS technology [C]. 2012 IEEE International Conference on Signal Processing, Computing and Control, IEEE, 2012: 1-5.

- [19] SHANDILAY R, SHARMA R K. High speed low power dual-edge triggered D flip-flop [C]. 2017 International Conference on Intelligent Computing and Control (12C2), IEEE, 2017: 1-5.

[20] DEVARAPALLI S V, ZARKESH-HA P, SUDDARTH S C. A robust and low power dual data rate (DDR) flip-flop using C-elements [C]. 2010 11th International Symposium on Quality Electronic Design (ISQED), IEEE, 2010: 147-150.

#### 作者简介

黄正峰,分别在 2000 年、2004 年和 2009 年于合肥工业大学获得学士学位、硕士学位和博士学位,现为合肥工业大学教授,主要研究方向包括超大规模集成电路设计与测试,纳米级 CMOS 集成电路抗辐射加固设计等。

E-mail: huangzhengfeng@ 139. com

**Huang Zhengfeng** received his B. Sc. degree, M. Sc. degree and Ph. D. degree all from Hefei University of Technology in 2000, 2004 and 2009, respectively. Now he is a professor at Hefei University of Technology. His main research interests include VLSI design and test, radiation hardening by design for the nano-scale CMOS integrated circuits and so on.

徐奇(通信作者),2012年于安徽大学获得学士学位,2018年于中国科学技术大学获得博士学位,现为合肥工业大学讲师,主要研究方向包括物理设计自动化和3D集成电路可靠性设计。

E-mail: xuqi@ hfut. edu. cn

Xu Qi (Corresponding author) received his B. Sc. degree from Anhui University in 2012, Ph. D. degree from University of Science and Technology of China in 2018. Now he is a lecturer at Hefei University of Technology. His main research interests include physical design automation and design for reliability for 3D integrated circuits.