· 112 ·

DOI: 10. 13382/j. jemi. B1902751

## 适用于 TIADC 时间误差校准的斩波调制算法\*

万祝娟<sup>1</sup> 尹勇生<sup>1,2</sup> 庞高远<sup>1</sup> 刘 涛<sup>3</sup> 谢熙明<sup>1</sup> 陈红梅<sup>1,2</sup> (1. 合肥工业大学 微电子设计研究所 合肥 230601; 2. 教育部 IC 设计网上合作研究中心 合肥 230601; 3. 中国电子科技集团公司第二十四研究所 重庆 400060)

摘 要:传统的时间交织模数转换器(TIADC)时间误差斩波调制校准算法无法向多通道推广,改进的时间误差斩波调制校准算法将单通道与相邻通道输出相加后分别斩波再求和来提取出时间误差,使其能适用于任意通道误差的提取,时间误差补偿采用一阶泰勒近似来实现,避免了传统算法中复杂滤波器设计。然而,当输入信号频率超过子通道奈奎斯特频率时,校准算法的校准方向会出错,从而导致校准失败。因此,设计了一种校准方向修正算法,能够满足整个系统奈奎斯特频率范围内的有效校准。仿真结果表明,应用于一个4通道、1 GS/s、12位的 TIADC,当输入信号频率为 450 MHz 时,系统的信号噪声畸变比(SNDR)由28.4 提高到73.1 dB,系统的无杂散动态范围(SFDR)由30.7 提高到88.9 dB。

关键词:时间交织模数转换器;数字校准;时间失配

中图分类号: TN432.1 文献标识码: A 国家标准学科分类代码: 510.3040

## Calibration technique for time-interleaved ADC using chopping modulation

Wan Zhujuan<sup>1</sup> Yin Yongsheng<sup>1,2</sup> Pang Gaoyuan<sup>1</sup> Liu Tao<sup>3</sup> Xie Ximing<sup>1</sup> Chen Hongming<sup>1,2</sup> (1. Institute of VLSI Design, Hefei University of Technology, Hefei 230601, China; 2. IC Design Web-Cooperation Research Center of MOE, Hefei 230601, China; 3. No. 24 Research Institute of CETC, Chongqing 400060, China)

Abstract: The traditional TIADC timing mismatch chopping modulation calibration cannot be extended to multi-channel. The improved timing mismatch chopping modulation calibration algorithm adds the single channel and the adjacent channel output to detect the timing mismatch. It can be applied to the detection of arbitrary channel timing mismatch. Compensation is implemented by first-order Taylor approximation, which avoids the complex filter design in traditional algorithms. However, when the input signal frequency exceeds the Nyquist frequency of sub-channel, the calibration direction of the calibration algorithm will be wrong, resulting in the failure of calibration system. Therefore, this paper proposed a new calibration direction correction algorithm that can meet the effective calibration of the Nyquist frequency range of the whole system. Simulation results show that when applied to a 4-channel, 1 GS/s, 12-bit TIADC and when the input signal frequency is 450 MHz, the signal-to-noise distortion ratio (SNDR) of the system is increased from 28.4 to 73.1 dB, and the spurious-free dynamic range (SFDR) is increased from 30.7 to 88.9 dB.

Keywords: analog to digital converter; all digital background calibration; timing mismatch

## 0 引 言

随着现代通信系统的快速发展,高速高精度时间交织模数转换器(time-interleaved ADC, TIADC)被广泛应用<sup>[1-4]</sup>。然而,TIADC的性能受到通道间失调、增益、时间

失配误差的影响。在前述的所有误差中,采样时间失配误差最关键,因为它随着输入频率增大而增大<sup>[5]</sup>。因此,本文的研究对象为时间误差的校准。

针对时间误差校准算法有很多<sup>[6-20]</sup>,其中,基于调制的采样时间误差校准算法因其简单、直观等优点,是校准算法的一个重要的分支,也是近些年的研究热点之一。

2002年, Jamal等[13]提出了一种数字校准算法,该算法基于斩波调制,校准两通道时间交织 ADC 中的失调、增益和时间失配误差,但是该技术只能用于两通道 TIADC,无法扩展到更多的通道。2010年, Law 等[14]将该调制技术扩展到四通道,但是补偿结构需要复杂的滤波器设计,且该算法受限于子奈奎斯特频带。2013年, Matsuno 等[15]利用 Hadamard 变换和 FIR 滤波器设计,设计了四通道TIADC 采样时间误差校准算法,但是设计复杂,可扩展性差。Duc 等[16-17]在2016年和2017年提出了一种基于调制的算法,并通过改进滤波器设计提高输入信号的带宽。然而,所需要的微分滤波器和希尔伯特滤波器大大增加了设计复杂度。

针对传统算法的不足,本文采用一种改进的时间误差斩波调制全数字校准算法。该算法利用单通道与相邻通道分别斩波后的输出之和提取误差系数,并通过一阶泰勒展开进行补偿。此外,本文设计实现了一种校准方向修正算法,通过分析复合输出及子通道输出的导数,判断导数符号一致性,以解决输入信号频带变化时校准方向可能出错的问题。本文提出的算法结构简单,不需要复杂的滤波器设计,适用于整个奈奎斯特频带,并且可以扩展到任意通道数的 TIADC 系统。

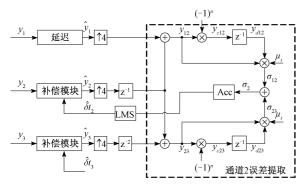

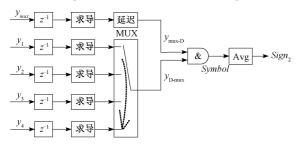

## 1 校准算法整体结构

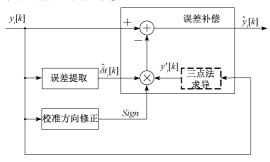

图 1 所示为本文校准算法的整体原理框图。其中, $y_i[k]$  为第 i 通道待校准的输出, $\hat{y}_i[k]$  为第 i 通道校准后的输出。误差提取模块采用改进的基于斩波调制的算法,其输出为  $\delta t_i[k]$ ,补偿算法基于一阶泰勒展开,校准方向修正模块输出 Sign,保证校准算法在整个奈奎斯特频率范围内能正确校准。

图 1 校准算法的整体原理框图

Fig. 1 The overall block diagram of calibration algorithm

## 2 采样时间误差估计

#### 2.1 传统的基于斩波调制的采样时间误差提取算法

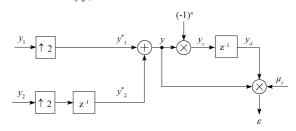

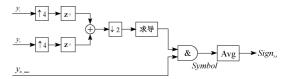

文献[13]最先提出了基于斩波调制的采样时间误差校准算法,图 2 所示为一个应用于两通道 TIADC 的采

样时间误差提取算法。设 TIADC 系统的采样频率为  $\omega_s$ ,输入信号的频率为  $\omega_0$ ,通道 1 的采样时间理想,通道 2 的采样时间误差为  $\delta t_2$ 。 将 TIADC 系统复合后的输出 y 乘以信号(-1)",该信号称为斩波信号,它以 TIADC 系统采样率+1、-1 交替。将 ADC 输出斩波得到  $y_e$ ,再经过一个延迟得到  $y_a$ 。

图 2 传统的采样时间误差提取算法[13]

Fig. 2 Block diagram of traditional sample-time error detection technique<sup>[13]</sup>

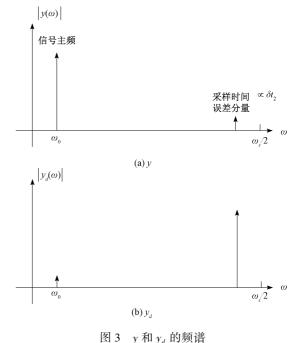

如图 3 所示,该相乘导致信号主频与杂散的位置互换。其次,输出 y 和斩波后的输出信号  $y_d$  在时域中相乘。得到的直流分量  $\varepsilon$  与时间误差  $\delta t_2$  的大小成正比,从而提取出通道二的时间误差,但该方法仅能实现二通道误差的提取。

图 5 y 和 y<sub>d</sub> 的 yy 盾

Fig. 3 Magnitude spectra for y and  $y_d$

以四通道 TIADC 为例,以第 1 通道为参考通道,需要提取出通道 2~4 的采样时间误差。根据文献[5]的分析,采样时间误差杂散频谱的位置出现在  $\omega$ ,/4  $\pm \omega$ 。以及  $\omega$ ,/2  $-\omega$ 0 处,当提取第 2 通道的时间误差时,位于  $\omega$ ,/4  $\pm$

$\omega_0$  处的杂散频谱相乘产生一个直流量,干扰误差检测,导致误差提取失败。因此,文献[13]的算法不能扩展至M(M>2)通道 TIADC,从而大大限制了其应用范围。

#### 2.2 改进的采样时间误差提取算法

TIADC 各子通道在时域上相隔一个时钟周期,但频域上表现为输出频谱有差异,因此需要依据 TIADC 的系统特性对不同通道的输出单独分析并设计误差提取算法,再归纳相同之处,减少重复设计,从而设计出简单有效的多通道 TIADC 时间误差提取方案。第 3、4 通道可以分别以第 1、2 通道为参考通道,所以第 3、4 通道的误差提取算法相同。改进的采样时间误差提取算法可以扩展至 M 通道 TIADC。

### 1)第2通道时间误差提取算法

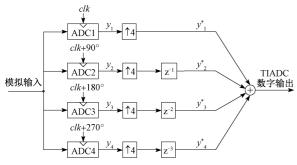

图 4 四通道 TIADC 的结构框图

Fig. 4 Block diagram of a four-channel TIADC architecture

图 4 所示为一个理想四通道 TIADC 的结构框图,各通道的采样时间误差均为 0。TIADC 系统的时钟周期为  $T_s$ ,输入信号为  $\sin \omega_0 t$ , 设第一通道和第二通道的样值之和为  $y_{12}$ , 则  $y_{12}$  只包含通道 1、2 的样值,不包含通道 3、4 的样值。即在  $T_s/2$ 、 $3T_s/2$  时刻的值等于  $\sin(\omega_0 t)$ ,在  $5T_s/2$ 、 $7T_s/2$  时刻的值等于 0。因此可得:

$$y_{12} = \sin(\omega_0 t) \times \left[ \frac{1}{\sqrt{2}} \times \left( \frac{\sqrt{2}}{2} + \sin(\omega_s t/4) \right) \right]$$

(1)

同理,设第 2 通道和第 3 通道的样值之和为  $y_{23}$ ,则只包含通道 2、3 的样值,不包含通道 3、4 的样值。即在  $T_s/2$ 、 $7T_s/2$  时刻的值等于 0,在  $3T_s/2$ 、 $5T_s/2$  时刻的值等于  $\sin(\omega_0 t)$ 。 因此可得:

$$y_{23} = \sin(\omega_0 t) \times \left[ \frac{1}{\sqrt{2}} \times \left( \frac{\sqrt{2}}{2} - \cos(\omega_s t/4) \right) \right]$$

(2)

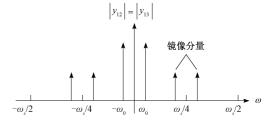

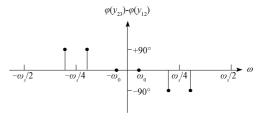

$y_{12}$  和  $y_{23}$  理想的幅度频谱如图 5 所示。

图 6 所示为  $y_{23}$  相对于  $y_{12}$  的相位频谱。  $y_{12}$  和  $y_{23}$  位于  $\omega_0$  处的相位相同,故相位差为 0。在  $\omega_s/4$   $\pm \omega_0$  处的相位 差为  $-90^\circ$ ,在  $-\omega_s/4$   $\pm \omega_0$  处的相位差  $+90^\circ$ ,这是因为实信号的相频曲线是奇对称的。

将  $y_{12}$  与  $y_{23}$  分别与  $(-1)^n$  =  $\pm 1$  相乘。使得频谱移 动  $\omega_s/2$ 。 经过斩波调制的信号与未经过斩波调制的信

图 5  $y_{12}$  和  $y_{23}$  理想的幅度频谱

Fig. 5 Ideal magnitude spectrum of  $y_{12}$  and  $y_{23}$

图 6  $y_{23}$  相对于  $y_{12}$  的相位频谱

Fig. 6 Plot of the change in the phase spectrum for  $y_{23}$  compared with  $y_{12}$

号相乘。在 $y_{23}$ 情况下, $+90^{\circ}$ 相移的分量与 $-90^{\circ}$ 相移的分量相乘,产生直流信号。 $y_{12}$ 情况与 $y_{23}$ 情况原理相同,只不过产生的直流信号的幅值相等,极性相反。因此,如果将 $y_{12}$ 和 $y_{23}$ 调制后的输出相加,直流项会抵消,从而避免了文献[13]的方法应用于四通道时直流项对误差提取的干扰。

改进的基于斩波调制的通道 2 采样时间误差提取算法实现框图如图 7 所示。 $y_1 - y_3$  是经过失调和增益校准后的输出。在通道 2 采样时间误差提取算法中,来自通道 2 的采样值与来自通道 1 和通道 3 的采样值分别相加,得到  $y_{12}$  和  $y_{23}$ 。 $y_{12}$  和  $y_{23}$  分别与斩波调制信号相乘,并经过延迟,然后再与  $y_{12}$  与  $y_{23}$  对应相乘,相乘结果与比例因子  $\mu_t$  相乘,得到  $\sigma_{12}$  和  $\sigma_{23}$ 。 $\sigma_{12}$  和  $\sigma_{23}$  相加,得到  $\sigma_{22}$  也有,相乘,得到  $\sigma_{23}$  也有,但是是估计值  $\delta t_2$ 。 $\delta t_2$  中没有来自  $\omega_s/4$   $\pm \omega_0$  处镜像分量的干扰。 $\delta t_2$  进入补偿模块。从而完成通道 2 的时间误差提取。

图 8 所示为当通道 2 的采样时间误差  $\delta t_2$  非 0 时, $y_{23}$  和  $y_{a23}$  的幅度频谱。与图 5 的  $y_{12}$  的频谱相同,在  $y_{23}$  的输出中, $\delta t_2$  会导致一个采样时间误差杂散分量出现在频率  $\omega_s/2-\omega_0$ 处,如图 8 (a) 所示。镜像分量同样出现在  $\omega_s/4\pm\omega_0$ 。  $y_{23}$  信号与  $y_{12}$  信号的处理方式相同,通过斩波调制 和延迟得到  $y_{d23}$ 。图 8 (b) 为  $y_{d23}$  频谱。 $y_{23}$  和  $y_{d23}$  相乘,在  $\omega_0$  处的输入和在  $\omega_s/2-\omega_0$  分量的乘积会产生一个非零 的直流分量,直流分量的极性与  $y_{12}$  情况下的相同。因 此,将此直流项与  $y_{12}$  情况下对应的直流项相加时,直流

图 7 通道 2 采样时间误差提取算法结构

Fig. 7 Block diagram of sample-time error detector for channel 2

项会相互增强。另一方面,  $y_{23}$  与 $y_{a23}$  中的镜像分量相乘, 会产生一个直流分量。它与  $y_{12}$  情况下的直流分量幅度相等、极性相反。因此,这两个直流分量相加会抵消,消除了来自镜像分量的干扰。留下的直流量来源于输入和误差分量,其大小与采样时间误差  $\delta t$ , 近似成比例。

图 8  $\delta t_2 \neq 0$  时的幅度频谱

Fig. 8 Magnitude spectra with  $\delta t_2 \neq 0$  for  $y_{23}$  and  $y_{d23}$

#### 2) 第 3、4 通道的误差提取算法

由图 4 及 TIADC 的时钟系统的特点可知,通道 3 的理想采样时刻恰好位于通道一采样时刻的中间,同理通道 4 的理想采样时刻恰好位于通道 2 采样时刻的中间。因此,分别以 1、2 通道为参考通道,使用文献[13]的算法,可以分别提取通道 3 和 4 的采样时间误差。以第 3 通道时间误差提取为例,原理如图 9 所示。

将图 4 的  $y_1^*$  和  $y_3^*$  相加,因为  $y_1^*$  和  $y_3^*$  的速率等于 4 通道 TIADC 的系统时钟,所以应该进行两倍的降采样,再用文献[13]的时间误差提取算法进行误差检测,得到

图 9 第 3 通道时间误差提取算法原理框图

Fig. 9 Block diagram of sample-time error detector for channel 3

通道3时间误差的估计值 $\delta t_3$ 。

改进的采样时间误差提取技术可扩展到并行的 4 个以上通道情况。对于一个八通道的 TIADC,第 2~4 通道的 采样时间误差用图 7 的方法提取,第 5~8 通道的采样时间误差用文献[13]的方式提取,参考通道为第 1~4 通道。

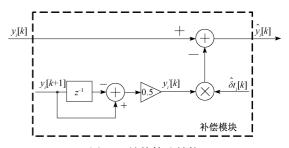

## 3 采样时间误差补偿

传统的时间误差补偿算法大多基于分数延迟滤波器的设计。滤波器的使用提高了设计难度,并且增加了校准算法的硬件消耗。因此,本文从数学分析角度,用一阶泰勒近似的方法设计出简单、有效的补偿算法。

含有时间误差的实际输出信号 y[k] 可以分解为理想输出信号 x[k] 与含有时间误差的多项式  $\sum_{k=1}^{M} e[n]$  之和,其中  $L(1 \le L \le M)$ , M为 TIADC 的通道数。如果能够从实际输出信号中消除含有时间误差的多项式,就可得到理想的输出信号。

利用一阶泰勒近似,可以得到第i 通道 ADC 经过补偿后的输出,如式(3)所示。

$$\hat{y}_{i}[k] = y_{i}[k] - \hat{\delta}t_{i}y'_{i}[k]$$

(3)

式中:  $y'_{i}[k]$  为第 $i$ 通道的实际采样信号对时间的一阶导数,可根据数值微分的方法得到,这里采用基于 3 点公式的拉格朗日插值多项式的一阶数值微分式估计  $y'_{i}[k]$ :

$$y'_{i}[k] \approx \frac{1}{2} \times (y_{i}[k+1] - y_{i}[k-1])$$

(4)

时间误差的补偿算法的整体框图如图 10 所示。

图 10 补偿算法结构

Fig. 10 Block diagram of compensation algorithm

## 4 校准方向修正

当输入信号频率超过子通道奈奎斯特频率时,误差

提取和补偿的方向可能发生变化,使得校准环路迭代方向错误,最终导致无法校准,因此需要对不同输入频率条件下的校准方向进行修正。

### 4.1 校准方向出错原因分析

从误差提取角度来看,对于第 2 通道 ADC 的时间误差提取而言,斩波调制时采用的时钟是整个 TIADC 系统的时钟,当输入信号在系统奈奎斯特频带内,误差提取的方向正确。当输入信号超过系统奈奎斯特频率,误差提取的方向与正确方向相反,导致误差提取算法出错;对于第 3、第 4 通道,在误差提取时均经历了 2 倍降采样,斩波调制的时钟与降采样后的时钟频率保持一致。所以误差提取算法只在系统奈奎斯特频率的 1/2(即归一化频率 0~0.25)带宽内有效,否则误差提取的方向相反,从而导致误差提取算法出错。

从误差补偿的角度来看,当补偿模块使用三点法公式进行求导时,求得的导数方向可能与实际方向相反。现象说明如图 11 所示。以一个四通道的 TIADC 为例,  $Slope_{(y[k])}$ 代表在 y[k]处实际的斜率,  $Slope_{(obtained)}$ 代表由三点法得到的斜率。

图 11 当输入信号位于不同的子奈奎斯特频带时, 采样序列和对应输入信号的导数

Fig. 11 Sampled sequences and corresponding derivative of input signals in different sub-NBs

当  $0 < f_{in} < f_s/8$  和  $f_s/4 < f_{in} < 3f_s/8$  时,三点法求得的导

数的符号与实际的相同; 当  $f_s$  /8 <  $f_{in}$  <  $f_s$  /4 和 3 $f_s$  /8 <  $f_{in}$  <  $f_s$  /2 <  $f_{in}$  <  $f_s$  , 求导方向分析与上述的类似。

根据上述的分析,可以总结校准方向随频带的变化规律,如表 1、2 所示。"+"表示校准方向与正确方向一致,"-"表示校准方向与正确方向相反。

表 1  $0 < f_m < f_s/2$ ,校准方向随输入信号频带的变化

Table 1 The calibration direction changing with  $0 < f_{in} < f_s/2$

| $f_{ m in}/f_s$ |      | $0 \sim \frac{1}{8}$ | $\frac{1}{8}$ $\sim$ $\frac{1}{4}$ | $\frac{1}{4} \sim \frac{3}{8}$ | $\frac{3}{8} \sim \frac{1}{2}$ |

|-----------------|------|----------------------|------------------------------------|--------------------------------|--------------------------------|

|                 | 提取   | +                    | +                                  | +                              | +                              |

| 第2通道            | 补偿   | +                    | -                                  | +                              | -                              |

|                 | 校准方向 | +                    | -                                  | +                              | -                              |

| 第 3、4 通道        | 提取   | +                    | +                                  | -                              | -                              |

|                 | 补偿   | +                    | -                                  | +                              | -                              |

|                 | 校准方向 | +                    | _                                  | -                              | +                              |

|                 |      |                      |                                    |                                |                                |

表 2  $f_s/2 < f_{in} < f_s$ ,校准方向随输入信号频带的变化

Table 2 The calibration direction changing with  $f_s/2 < f_{in} < f_s$

| $f_{\rm in}$ | $f_s$ | $\frac{1}{2} \sim \frac{5}{8}$ | $\frac{5}{8} \sim \frac{3}{4}$ | $\frac{3}{4} \sim \frac{7}{8}$ | <del>7</del> ~ 1 |

|--------------|-------|--------------------------------|--------------------------------|--------------------------------|------------------|

|              | 提取    | -                              | -                              | -                              | -                |

| 第2通道         | 补偿    | +                              | -                              | +                              | -                |

|              | 校准方向  | -                              | +                              | -                              | +                |

| 第 3、4 通道     | 提取    | +                              | +                              | -                              | -                |

|              | 补偿    | +                              | -                              | +                              | -                |

|              | 校准方向  | +                              | -                              | -                              | +                |

从表 1 和 2 可以看出,当输入信号频率在  $0 < f_{in} < f_s / 8$ 时,所有通道的校准方向都正确,故校准算法有效工作。其他频带内,校准方向出错,导致校准算法失效。当输入信号频率超过 $f_s / 2$  时,校准方向也会随着 $f_{in}$  改变。因此需要校准方向修正算法,自适应地修正校准方向,否则 $\delta t_i$  不会收敛。

#### 4.2 校准方向修正算法

以四通道 TIADC 为例,因为第 2 通道校准方向变化的规律与文献[18]一致。因此,可以将文献[18]提出的校准方向修正算法应用于第二通道。该算法的原理如式(5)所示。

$Symbol = sign(y_{D-mux}) & sign(y_{mux-D})$  (5) 式中: $y_{D-mux}$  表示第 1~4 子通道先单独求导再复合的值,而  $y_{mux-D}$  表示第 1~4 子通道先复合再求导的值。  $sign(y_{D-mux})$  表示  $y_{D-mux}$  的符号, $sign(y_{mux-D})$  表示  $y_{mux-D}$  的符号,& 表示"与"操作。

当输入信号的频率为  $0 < f_{in} < f_s/8$  或  $f_s/4 < f_{in} < 3f_s/8$  时,  $sign(y_{D-mux})$  与  $sign(y_{mux-D})$  总是保持相同的极性, Symbol 的值始终为 1,将 Symbol 的值反馈回校准系统,不会改变校准方向。而根据 4.1 节的分析, 当输入信号的

频率为 $0 < f_{in} < f_s / 8$  或 $f_s / 4 < f_{in} < 3 f_s / 8$  时,第 2 通道校准方向是正确的,实际上也不需要改变校准方向,因此这种情况下校准方向修正算法不会影响系统的正常工作。当输入信号的频率为 $f_s / 8 < f_{in} < f_s / 4$  或  $3 f_s / 8 < f_{in} < f_s / 2$  时,sign  $(y_{D-mux})$  与 sign  $(y_{mux-D})$  总是保持相反的极性,Symbol 的值为-1。根据 4.1 节的分析,第 2 通道的原校准方向是错误的,而与 Symbol 相乘后,修正后的校准方向会与原校准方向相反,恰好回到正确的方向上。因此该算法能够修正第 2 通道的校准方向。

算法的实现框图如图 12 所示。其中, y<sub>mux</sub> 是 TIADC 系统的输出, 求导模块利用三点公式求出导数, MUX 是 复合模块, & 是与门, Avg 是指数平均器模块, 起到优化的作用, 将优化后的值 Sign<sub>2</sub> 反馈回校准系统就能修正错误的校准方向, 并且不改变正确的校准方向。

图 12 第 2 通道校准方向修正算法框图

Fig. 12 Block diagram for calibration direction correction algorithm for channel 2

加入了校准方向修正算法后,校准方向随频带的变化如表 3、4 所示。由表 3、4 可见,校准系统在整个奈奎斯特频带内有效,当超过系统奈奎斯特频率时,依然有效。

# 表 3 $0 < f_{in} < f_{s}/2$ ,修正后的第2通道校准方向 随输入信号频带的变化

Table 3 The proposed algorithm for channel 2 changing with normalized input frequency  $f_{in}/f_s$  in nyquist band

| $f_{\rm in}/f_{\rm s}$ | 0~1 | 1 ~ 1 | 1~3 | 3~1 |

|------------------------|-----|-------|-----|-----|

|                        | 8   | 8 4   | 4 8 | 8 2 |

| 校准方向                   | +   | -     | +   | -   |

| Symbol                 | +   | -     | +   | -   |

| 修正后的校准方向               | +   | +     | +   | +   |

表 4  $f_s/2 < f_{in} < f_s$ ,修正后的第2通道校准方向 随输入信号频带的变化

Table 4 The proposed algorithm for channel 2 changing with normalized input frequency  $f_{in}/f_c$  over nyquist band

| $f_{ m in}/f_s$ | $\frac{1}{2} \sim \frac{5}{8}$ | $\frac{5}{8} \sim \frac{3}{4}$ | $\frac{3}{4} \sim \frac{7}{8}$ | $\frac{7}{8}$ ~1 |

|-----------------|--------------------------------|--------------------------------|--------------------------------|------------------|

| 校准方向            | -                              | +                              | -                              | +                |

| Symbol          | -                              | +                              | -                              | +                |

| 修正后的校准方向        | +                              | +                              | +                              | +                |

因为第3、4通道校准方向变化的规律与第2通道不一致,故不能采用文献[18]中校准方向修正算法。因此,本文提出了一种改进的校准方向修正算法,原理如式(6)所示。

$Symbol = sign(y_{D-mux}) & sign(y_{24-D})$  (6) 式中: $y_{D-mux}$  表示第 1~4 子通道先单独求导再复合的值, $sign(y_{D-mux})$  表示  $y_{D-mux}$  的符号, $y_{24-D}$  表示第 2 和第 4 通道复合后再经过 2 倍降采样后再求导的值, $sign(y_{24-D})$  表示  $y_{24-D}$  的符号,& 表示"与"操作。

当输入信号的频率为  $0 < f_{in} < f_s/8$  或  $3f_s/8 < f_{in} < f_s/2$  时, $sign(y_{D-mux})$  与  $sign(y_{24-D})$  总是保持相同的极性, Symbol 的值始终为 1,将 Symbol 的值反馈回校准系统,不 会改变校准方向。而根据 4. 1 节的分析,当输入信号的 频率为  $0 < f_{in} < f_s/8$  或  $3f_s/8 < f_{in} < f_s/2$  时,第 3、4 四通道的校准方向是正确的,实际上也不需要改变校准方向,因此这种情况下校准方向修正算法不会影响系统的正常工作。 当输入信号的频率为  $f_s/8 < f_{in} < f_s/4$  或  $f_s/4 < f_{in} < 3f_s/8$  时,  $sign(y_{D-mux})$  与  $sign(y_{24-D})$  总是保持相反的极性, Symbol 的值为 -1。根据 4. 1 节的分析,第 3、4 通道的原校准方向是错误的,而与 Symbol 相乘后,修正后的校准方向会与原校准方向相反,恰好回到正确的方向上。 因此该算法能够修正第 3、4 通道的校准方向。

算法的实现框图如图 13 所示。 $y_2$  和  $y_4$  分别是第 2 通道 ADC 和第 4 通道 ADC 的输出,进行 4 倍上采样,对齐时序并复合。复合后的时钟速率是 TIADC 系统的时钟速率,而需要求导的符号变化与系统奈奎斯特频率的 1/2 (即归一化频率等于 0. 25) 有关,因此首先需要进行 2 倍降采样,然后再进行三点法求导,得到  $y_{24D}$  。yD-mux 来自于第 2 通道校准方向修正算法,不需要重复求取,从而减少硬件消耗。& 是与门,Avg 是指数平均器模块,起到优化的作用,将优化后的值  $Sign_{3,4}$  反馈回校准系统就能修正错误的校准方向,并且不改变正确的校准方向。

图 13 第 3、4 通道校准方向修正算法框图

Fig. 13 Block diagram for calibration direction correction algorithm for channel 3 and channel 4

加入了校准方向修正算法后,校准方向随频带的变化如表5、6 所示。由表5、6 可见,校准系统在整个奈奎斯特频带内有效,当超过系统奈奎斯特频率时,依然有效。

## 表 5 $0 < f_{in} < f_{s}/2$ ,修正后的第 3、4 通道校准方向 随输入信号频带的变化

Table 5 The proposed algorithm for channel 3 and channel 4 changing with normalized input frequency  $f_{in}/f_s$  in nyquist band

| $f_{ m in}/f_s$ | 0~1/8 | $\frac{1}{8} \sim \frac{1}{4}$ | $\frac{1}{4} \sim \frac{3}{8}$ | $\frac{3}{8} \sim \frac{1}{2}$ |

|-----------------|-------|--------------------------------|--------------------------------|--------------------------------|

| 校准方向            | +     | -                              | -                              | +                              |

| Symbol          | +     |                                |                                | +                              |

| 修正后的校准方向        | +     | + +                            |                                | +                              |

结合第2通道校准方向修正算法和第3、4通道校准 方向修正算法,校准系统在整个奈奎斯特频带内有效,当 超过系统奈奎斯特频率时,依然有效。因此,校准方向修 正算法大大提高了整个校准系统的适用带宽。

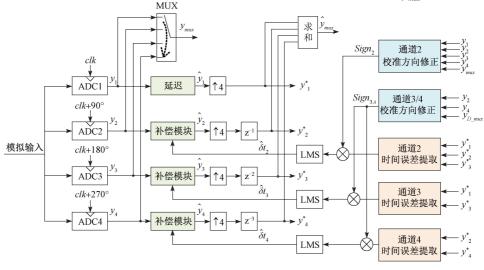

加入了校准方向修正算法后的校准系统的整体结构

## 表 6 $f_s/2 < f_{in} < f_s$ ,修正后的第 3、4 通道校准方向 随输入信号频带的变化

Table 6 The proposed algorithm for channel 3 and channel 4 changing with normalized input frequency  $f_{\rm in}/f_s$  over nyquist band

| $f_{ m in}/f_s$ | $\frac{1}{2} \sim \frac{5}{8}$ | $\frac{5}{8} \sim \frac{3}{4}$ | $\frac{3}{4} \sim \frac{7}{8}$ | <del>7</del> ~ 1 |

|-----------------|--------------------------------|--------------------------------|--------------------------------|------------------|

| 校准方向            | +                              | -                              | -                              | +                |

| Symbol          | +                              | -                              | -                              | +                |

| 修正后的校准方向        | +                              | +                              | +                              | +                |

框图如图 14 所示。其中  $y_1 - y_4$  进入 MUX 模块,得到复合后的输出  $y_{\text{mux}}$  , $y_{\text{mux}}$  是通道 2 校准方向修正模块的输入。  $y_1 - y_4$  经过补偿后分别得到  $\hat{y}_1 - \hat{y}_4$ ,再经过 4 倍上采样和延迟对齐后得到  $y_1^* - y_4^*$ ,将  $y_1^* - y_4^*$  四路数据相加即得到校准后的系统输出  $\hat{y}_{\text{mux}}$ 。

图 14 TIADC 校准系统整体结构框图

Fig. 14 The overall block diagram of TIADC calibration system

## 5 仿真结果

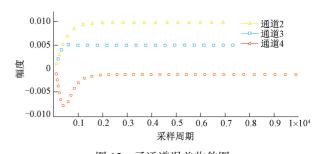

以 MATLAB/Simulink 为仿真验证平台,对本文所提算法进行行为级验证,设置 12 bits、四通道 TI-ADC,系统频率为 1 GHz,各个子通道的时间误差设置为[0,0.03,0.015,-0.004] T<sub>s</sub>。当输入信号归一化频率为 0.1,第 2~4 通道误差收敛图如图 15 所示。可以看出,第三通道的误差提取最快,约在 10 000 个时钟周期后完成,因为第 3 通道仅以第 1 通道为参考。第 2 通道的误差提取约在 25 000 个时钟周期后完成,在第 2 通道误差提取收敛后,大约又经过了额外的 5 000 个时钟周期后,第 4 通道误差提取完成。

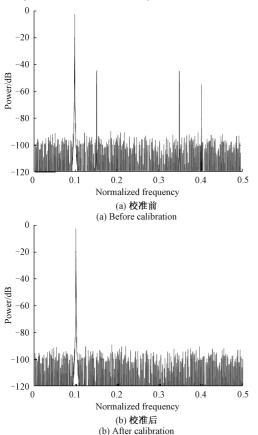

校准前后的 FFT 频谱图如图 16 所示,可以看出,通过校准, SNDR 从校准前的 41.6 dB 提升到校准后的

图 15 子通道误差收敛图

Fig. 15 Convergence speed of timing mismatch estimation

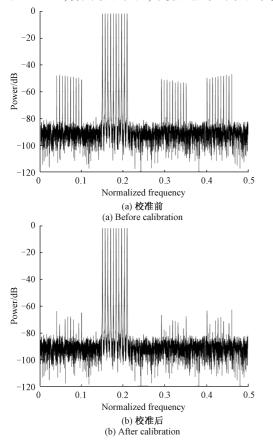

73. 3 dB, SFDR 从校准前的 43.9 dB 提升到校准后的 89.0 dB, ENOB 从校准前的 6.61 bits 提升到校准后的 11.89 bits。当输入信号为归一化频率为 0.45,校准前后的 FFT 频谱图如图 17 所示,对比校准前后结果, SNDR由 28.4 提升到 73.1 dB, SFDR由 30.7 提升到 88.9 dB,

ENOB 由 4.42 提升到 11.85 bits, TIADC 系统的动态性能得到提高,证明了本算法有效性。

图 16  $f_{in}/f_s = 0.1$  低频输入时校准前后的 FFT 频谱图 Fig. 16 Simulation results with low-frequency input when  $f_{in}/f_s = 0.1$

当输入信号频率位于不同的子奈奎斯特频带时,SNDR和 SFDR与归一化频率的关系如图 18 所示。可以看出,校准前的 SFDR和 SNDR随着输入信号频率的增加而降低。这是因为采样时间失配对 TIADC 系统性能的影响随输入频率的增加而增大。当输入信号频率超过系统奈奎斯特频率时,SFDR略有降低,这是因为采用一阶泰勒近似来获得式(6),当输入频率增加时,这种近似变得不太精确,但所提出的校准算法仍然可以正常工作。在前四个子奈奎斯特频带内,所提出的校准算法将SFDR提高了至少 45 dB,证明了本文所提出的校准算法的有效性。

对多频率混合输入信号进行的仿真验证,对于四通道的 TI-ADC,设置通道间的时间误差为[0,0.05,0.01, -0.004]  $T_s$ ,多频输入信号的最低频率为  $f_L$  = 0.15 ·  $f_s$  + 0.059 ·  $f_s$ ,最高频率为  $f_H$  = 0.5 ·  $f_s$  + 0.59 ·  $f_s$ , 最高频率为  $f_H$  = 0.5 ·  $f_s$  + 0.59 ·  $f_s$ , 损率间隔为 0.059  $f_s$ , 仿真结果如图 19 所示,其中图 19(a)为校准前的频率图,图 19(b)为校准后的频率图,可以看出,在

图 17  $f_{\text{in}}/f_{\text{s}}$  = 0. 45 高频输入时校准前后的 FFT 频谱图

Fig. 17 Simulation results with high-frequency input when  $f_{in}/f_s = 0.45$

图 18 输入信号的频率对校准效果的影响

SNDR/SFDR vs. input frequencies over the sub-NBs

Fig. 18

校准前,多频输入信号有明显的杂散频谱,校准后,杂散频谱得到显著消除,SFDR 由校准前的 42.3 dB 提升到校准后的 60.1 dB,仿真结果表明,本算法能够有效校准。

图 19 多频信号的校准前后对比

Fig. 19 Simulation results with multi tones input

表7为本文与其他调制算法的对比结果。可以看出,本文设计的校准算法,是一种全数字校准算法,不需要复杂的滤波器设计,能够实现任意频带内输入信号的校准,且可以扩展至任意通道。

表 7 本文与其他代表算法的对比

Table 7 Comparison with the state-of-the-art techniques

| 特点     | 文献[13] | 文献[14] | 文献[15] | 文献[16] | 文献[18] | 本文 |

|--------|--------|--------|--------|--------|--------|----|

| 全数字    | 是      | 是      | 是      | 是      | 是      | 是  |

| 宽带宽    | 否      | 否      | 否      | 否      | 是      | 是  |

| 滤波器    | 是      | 是      | 是      | 是      | 是      | 否  |

| 通道数    | 2      | 4      | 2      | 4      | 4      | 4  |

| 位数/bit | 10     | 11     | 10     | 11     | 12     | 12 |

## 6 结 论

本文采用了一种改进的基于斩波调制的时间失配误 差算法提取误差系数,补偿模块基于一阶泰勒展开。为 了扩展校准算法的适用带宽,本文提出了一种校准方向修正算法,解决了输入信号频带变化时校准方向可能出错的问题。本文提出的算法结构简单,不需要复杂的滤波器设计,适用于整个奈奎斯特频带,并且可以扩展到任意通道数的 TIADC 系统。在前 4 个子奈奎斯特频带内,对单频输入信号的 SFDR 提高了至少 45 dB,校准效果理想。

## 参考文献

- [ 1 ] RAZAVI B. Design considerations for interleaved ADCs[J].

IEEE Journal of Solid-State Circuits, 2013, 48 (8):

1806-1817.

- [ 2 ] STRAAYER M, BALES J, BIRDSALL D, et al. A 4GS/ s time-interleaved RF ADC in 65nm CMOS with 4GHz input bandwidth [ C ]. IEEE International Solid-State Circuits Conference, 2016; 464-466.

- [ 3 ] NAM J W, HASSANPOURGHADI M, ZHANG A Y, et al. A 12-Bit 1.6, 3.2, and 6.4 GS/s 4-b/cycle time-interleaved SAR ADC with dual reference shifting and interpolation [ J ]. IEEE Journal of Solid-State Circuits, 2018, 53(6); 1765-1779.

- [4] 杨扩军, 田书林, 蒋俊,等. 基于 TIADC 的 20 GS/s 高速数据采集系统[J]. 仪器仪表学报, 2014, 35(4): 841-849.

YANG K J, TIAN SH L, JIANG J, et al. 20 GSPS high speed data acquisition system based on TIADC [J].

Journal of Electronic Measurement and Instrument,

[5] 叶凡. 多通道时间交织模数转换器的校正与集成电路实现方法研究[D]. 上海: 复旦大学, 2010: 1-146. YE F. Research of multi-channel calibration algorithm for time interleaved analog-to-digital converter and integrated circuit implementation [D]. Shanghai: Fudan University, 2010: 1-146.

2014, 35(4): 841-849.

- [6] EL-CHAMMAS M, MURMANN B. A 12 GS/s 81-mW 5-bit time-interleaved flash ADC with background timing skew calibration [J]. IEEE Journal of Solid-State Circuits, 2011, 46(4): 838-847.

- [7] DORIS K, JANSSEN E, NANI C, et al. A 480mW 2.6GS/s 10b 65nm CMOS time-interleaved ADC with 48.5dB SNDR up to nyquist [C]. IEEE International Solid-State Circuits Conference. 2011: 180-182.

- 8 STEPANOVIC D, NIKOLIC B. A 2.8 GS/s 44.6 mW time-interleaved ADC achieving 50.9 dB SNDR and 3 dB effective resolution bandwidth of 1.5 GHz in 65 nm CMOS[J]. IEEE Journal of Solid-State Circuits, 2013, 48(4): 971-982.

- [ 9 ] LIU H S, XU H. An adaptive blind frequency response

[12]

mismatches calibration method for four-channel TIADCs based on channel swapping [J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2016, 64(6): 625-629.

- [10] REYES BT, SANCHEZ RM, POLA AL, et al. Design and experimental evaluation of a time-interleaved ADC calibration algorithm for application in high-speed communication systems [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2017,64(5): 1019-1030.

- [11] 陈红梅, 黄超, 邓红辉,等. 带参考通道的时间交叉 ADC 数字后台校准方法[J]. 电子测量与仪器学报, 2015, 29(12): 1739-1745.

CHEN H M, HUANG C, DENG H H, et al. Background digital calibration method for time-interleaved ADC using A reference ADC[J]. Journal of Electronic Measurement and Instrumentation, 2015, 29(12): 1739-1745.

- 失配校准方法[J]. 国外电子测量技术, 2016, 35(4): 34-37.

XIANG Q, LIU H Q, BAO S Y. Correction method for channel mismatches errors in TIADC system based on the principle of equivalent sampling[J]. Foreign Electronic Measurement Technology, 2016, 35(4): 34-37.

向前, 刘洪庆, 包思云. 基于等效采样的 TIADC 通道

- [13] JAMAL S M, FU D, SINGH M P, et al. Calibration of sample-time error in a two-channel time-interleaved analog-to-digital converter [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2004, 51(1): 130-139.

- [14] LAW C H, HURST P J, LEWIS S H. A four-channel time-interleaved ADC with digital calibration of interchannel timing and memory errors [J]. IEEE Journal of Solid-State Circuits, 2010, 45(10): 2091-2103.

- [15] MATSUNO J, YAMAJI T, FURUTA M, et al. All-digital background calibration technique for time-interleaved ADC using pseudo aliasing signal [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2013, 60(5):1113-1121.

- [16] DUC H L, NGUYEN D, JABBOUR C, et al. All-digital calibration of timing skews for TIADCs using the polyphase decomposition [J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2016, 63(1): 99-103.

- [17] DUC H L, NGUYEN D, JABBOUR C, et al. Fully digital feedforward background calibration of clock skews for sub-sampling for TIADCs using the polyphase

- decomposition [J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2017, 64(6): 1515-1528.

- [18] 吴景生、TI-ADC 数字校准技术研究[D]. 合肥, 合肥 工业大学, 2018: 1-96. WU J SH. Research of digital calibration algorithm for time-interleaved ADCs[D]. Hefei; Hefei University of

- Technology, 2018:1-96.

[19] 闫辉, 邓红辉, 万祝娟,等. 误差提取自适应修正的前馈式 TIADC 校准算法[J]. 电子测量与仪器学报,

- 2019, 33(6): 171-176.

YAN H, DENG H H, WAN ZH J, et al. Adaptive fully digital feedforward calibration algorithm of timing mismatch for sub-sampling TIADCs [J]. Journal of Electronic Measurement and Instrumentation, 2019, 33(6): 171-176.

- [20] 甘凌浩, 尹勇生, 孙康康,等. 一种适用于多频输入的 TIADC 时间失配误差校准方法[J]. 电子测量与仪器 学报, 2019, 33(10): 134-141. GAN L H, YIN Y S, SUN K K, et al. Calibration method aimed at multitone input for timing mismatch in TIADC [J]. Journal of Electronic Measurement and Instrumentation, 2019, 33(10): 134-141.

#### 作者简介

万祝娟,2018年于合肥工业大学学士 学位,现为合肥工业大学硕士研究生,主要 研究方向为混合信号电路设计。

E-mail: hmchen@ hfut. edu. cn

**Wan Zhujuan** received the B. Sc. degree from Hefei University of Technology in 2018.

She is currently a M. Sc. candidate at Hefei University of Technology. Her main research interest includes mixed signal processing.

陈红梅,2008年于华中科技大学获得学士学位,2011年于华中科技大学获得硕士学位,2017年于中国科学技术大学获得博士学位,现为合肥工业大学讲师,主要研究方向为CMOS混合信号电路,A/D和D/A转换器,传感器接口。

E-mail: hmchen@ hfut. edu. cn

Chen Hongmei received her B. Sc. degree from Huazhong Science & Technology University in 2008 and M. Sc. degree from Huazhong Science & Technology University in 2011, and Ph. D. degree from University of Science & Technology of China in 2017. Now she is a lecturer at Hefei University of Technology. Her main research interests include CMOS mixed-signal circuits, A/D and D/A converters, and sensor interface.