DOI: 10. 13382/j. jemi. B2407180

# 面向 FPGA-TDL-TDC 的延迟时间逐位校准网络\*

许 玥<sup>1,2</sup> 谢 杰<sup>1</sup> 曾中明<sup>1,2</sup> 张宝顺<sup>1,2</sup> 吴东岷<sup>1,2</sup>

- (1. 中国科学技术大学纳米技术与纳米仿生学院 合肥 230026;

- 2. 中国科学院苏州纳米技术与纳米仿生研究所 苏州 215123)

摘 要:时间数字转换器(TDC)是一种将信号脉冲之间时间间隔的连续模拟量转换为离散数字量的设备。基于现场可编程逻辑门阵列(FPGA)内部进位链资源实现抽头延迟链-时间数字转换器(TDL-TDC)的方法被广泛应用,但 TDL-TDC 中每个延迟单元的延迟时间数值受运行温度变化的影响较大,目前使用码密度测试、线性补偿或高阶泰勒函数拟合等的 TDC 校准方法不能很好地拟合复杂温度变化情况下长延迟链中各单元延迟时间的变化趋势。为继续满足 TDC 工作精度要求,提出了一种基于多层感知机(MLP)的神经网络校准方案,以延迟链中 128 个延迟单元的延迟时间数据和相应温度数据作为训练样本建立 4层MLP。工作时通过反馈当前运行温度信息,可以独立给出每个延迟单元的延迟时间数值,以用于计算待测脉冲之间的时间间隔。实验验证了校准网络对温度变化的补偿作用,该网络可以移植于不同的 FPGA 芯片。测量得到校准网络的准确率为 91%,实现 TDC 分辨率为 34 ps。

关键词: 现场可编程逻辑门阵列;抽头延迟链-时间数字转换器;多层感知机;神经网络校准

中图分类号: TN79; TP391 文献标识码: A 国家标准学科分类代码: 520.6099

# Bin-by-bin network calibration for delay time of FPGA-TDL-TDC

Xu Yue<sup>1,2</sup> Xie Jie<sup>1</sup> Zeng Zhongming<sup>1,2</sup> Zhang Baoshun<sup>1,2</sup> Wu Dongmin<sup>1,2</sup>

- (1. School of Nano-Tech and Nano-Bionics, University of Science and Technology of China, Hefei 230026, China;

- 2. Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, Suzhou 215123, China)

Abstract: The time-to-digital converter (TDC) is a device designed to convert the continuous analog value of time interval between signal pulses into discrete digital values. The tapped-delay-line time-to-digital converter (TDL-TDC) is commonly implemented using the internal carry chain resources of field programmable gate array (FPGA) chips. However, the delay time of each delay bin in the TDL-TDC is significantly impacted by variations in operating temperature. Currently, methods of TDC calibration, such as code density calibration, linear compensation, or high-order Taylor function fitting, struggle to accurately model the changing delay times of individual bins within a long delay line under varying temperature conditions. To maintain the required precision of TDC operations, a neural network calibration based on multilayer perceptron (MLP) is proposed. This method utilizes delay time and corresponding temperature data from 128 delay bins in the delay line as training data to construct a four-layer MLP. By feeding back temperature information when working, the network can independently calculate delay time of different bin to determine the time interval between signal pulses. Experimental results confirm the effectiveness of the network calibration in compensating for temperature variations, with the potential for deployment across different FPGA chips. The network achieves an accuracy of 91%, and the resolution of TDC is 34 ps.

Keywords: FPGA; TDL-TDC; multilayer perceptron; neural network calibration

# 0 引 言

时间数字转换器(time-to-digital converter, TDC)能够 检测到两个信号脉冲之间的时间间隔长短,并将该时间 信息转换为离散的数字量用于后续处理,被广泛应用于 激光雷达、声纳、遥感成像等需要测量未知时间间隔的领 域[1]。通常,TDC 可以通过两种方式实现:专用集成电路 (application specific integrated circuit, ASIC)和现场可编 程逻辑门阵列(field programmable gate array, FPGA)[2-5]。 FPGA 是一种可编辑内部逻辑电路的设计芯片,具有高 度可定制性和灵活性。在过去的几年时间里,FPGA 技 术表现出巨大的进步,使得 FPGA 能够缩小与 ASIC 在性 能上的差距,促使越来越多的研究致力于利用 FPGA 架 构来实现 TDC 系统[6]。FPGA-TDC 通过将高分辨率 TDC 体系结构与粗计数器配合,利用 FPGA 内部逻辑单 元产生的延迟时间,或者以不同频率时钟的相位之差,作 为更小的时间单位来划分待测时间间隔,从而达到超越 最高时钟周期的测量精度[7]。TDC分辨率取决于其内部 结构更准确地划分和测量时间的能力[8-9]。利用多相位 时钟采样法、游标法等原理设计的 TDC,能够达到的最优 测量分辨率与系统内部运行频率密切相关[10-12],而基于 FPGA 芯片内部延迟单元搭建的 TDC(例如抽头延迟链-时间数字转换器)可以突破时钟频率的限制,实现更高精 度的 TDC 功能<sup>[13]</sup>。

由于运行时温度状态的不同,TDC 最低有效位(least significant bit,LSB)并非固定不变的,这会导致实际转换 曲线与理想曲线在量化步进值上的不一致。目前,针对 温度因素变化所带来的影响,基于 FPGA 的抽头延迟链-时间数字转换器(tapped-delay-line time-to-digital converter, TDL-TDC) 主要依赖于在 FPGA 内部构建码密 度校准模块[14],实现对 TDC 内部单元延迟时间的校准。 码密度校准法校准时间较长,会导致系统运行时出现过 长的死区时间。同时,由于 TDL-TDC 内部延迟单元的延 迟时间受运行温度变化影响严重,往往需要进行大量的 片上校准才能继续满足工作精度要求,这将进一步加剧 上述问题。考虑到温度变化造成 LSB 不一致性,改善的 TDL-TDC 系统常采用线性系数修正或者高阶泰勒函数 拟合温度变化影响曲线的方式进行补偿[15-16]。当延迟链 不同位置上不同延迟单元随温度的变化趋势不一致时, 或者所需的运行温度范围较大时,或者期望在较小的温 度变化范围内得到更好的变化趋势拟合结果时,上述方 法人工计算量大且不能很好地拟合长延迟链上不同位置 的变化趋势。

基于 FPGA 的 TDC 研究工作都提出了 TDC 作为系统应用的一部分,为了完成系统整体功能,FPGA 数据采

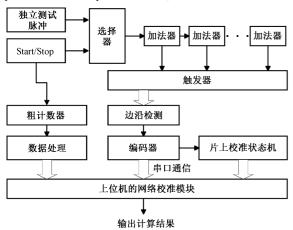

集系统的工作结果通常需要传输至上位机,配合相关处理算法进一步计算[17-20]。针对上述问题结合上位机的使用,本文创新的提出了一种基于神经网络的 TDC 校准方案。该方案分别在 FPGA 芯片和上位机搭建片上校准模块和网络校准模块,将 TDC 各延迟单元的延迟时间数据和相应的运行温度信息传输至上位机。上位机利用延迟时间和对应运行温度数据作为原始样本进行训练,得到训练好的网络结构作为网络校准模块的结果。实际工作时,反馈运行条件下的不同温度数值传输至上位机,通过训练好的网络模块可以直接从上位机中获取不同温度情况时,TDC 不同延迟单元经过校准的延迟时间数值,用于后续计算过程。

为了验证该方案的可行性,实验分别采用ep4ce30f23c8 FPGA和ep4ce115f23i7 FPGA芯片设计搭建了基于加法器进位延迟链的TDL-TDC结构以及相关处理和传输模块。实验时,将TDC放入温度可控的恒温箱中,改变恒温箱温度并反复测量。通过片上的码密度测试采集不同温度条件下TDC各个延迟单元的延迟时间信息用作训练数据,并在上位机上构建多层感知机(multilayer perceptron,MLP)结构来训练延迟时间与温度之间的函数关系。

本文给出搭建的 FPGA-TDL-TDC 系统原理和结构设计、采用 MLP 的上位机校准模块原理和结构设计及 TDC 温度实验过程和相关实验结果,实验验证网络校准 的可行性。从本文搭建的系统中可以看到,建立在上位 机的网络校准模块可以应用于不同类型的 FPGA 芯片,可以补偿温度因素对 TDC 的影响。同时,提出了一种 TDC 应对复杂变化影响的可行方案。

# 1 FPGA-TDL-TDC 原理和结构

#### 1.1 TDC 测量原理

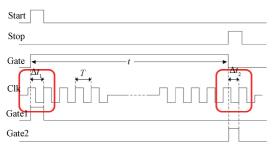

当待测时间间隔的开始和结束两个脉冲标志信号 (Start 和 Stop 信号) 到达 TDC 的接收端后,被传送进入 粗时间计数器模块。粗时间计数器模块使用 193 MHz 的时钟频率,搭建两个反相的格雷码计数器来测量待测脉冲之间的粗略时间间隔  $t_{coarse}$ 。但,由于计数器开始计数时钟边沿和结束计数时钟边沿,与 Start 和 Stop 标志信号脉冲边沿存在小的时间间隔,如图 1 中的  $\Delta t_1$  和  $\Delta t_2$  所示。为达到超越时钟周期的计算精度,需要利用 FPGA内部的高分辨率体系结构实现更精确的测量。待测时间间隔 t 计算公式为:

$$t = t_{\text{coarse}} + \Delta t_1 - \Delta t_2 \tag{1}$$

$$t_{\text{coarse}} = N \cdot T \tag{2}$$

#### 1.2 FPGA-TDL-TDC 的细时间测量模块

FPGA 芯片中的进位链提供了一种可以实现加法快

图 1 TDC 测量原理

Fig. 1 The diagram of TDC measurement

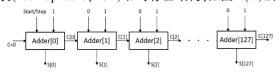

速进位运算的结构。搭建 TDL-TDC 的延迟链需要利用 FPGA 内部逻辑单元(logic element, LE)间的短传播延迟时间,和进位链阵列的规则排布结构来构造实现。实验分别在 Cyclone IV 的两款 FPGA 芯片 ep4ce30f23c8 和 ep4ce115f23i7 上连接了 128 个加法器,建立起工作频率为 193 MHz 的抽头延迟链结构,并将延迟链固定在 FPGA 芯片上的适当位置,以确保最小的走线延迟。 Ep4ce30f23c8 FPGA 中搭建的加法延迟链原理结构如图 2(a)所示。Ep4ce30f23c8 内部每个逻辑阵列块(logic array block, LAB)包括 16 个 LE,如图 2(b)所示。本系统TDC 搭建使用了 8 个 LAB,每个 LE 内部具有进位链、查找表(look-up-table, LUT)和寄存器结构,如图 2(c)所示。

### (a)加法器构建的延迟链结构 (a)The structure of delay line connected by adders

Fig. 2 The structure of delay line

除延迟链上第1个加法器的两个输入端输入 start/stop 信号和1,其他 127个加法器的两个输入端均输入 0和1。当 start/stop 信号端输入为 0时,加法链上所有加法器输出为全1。当传入第1个加法器的 start/stop 信号

值由 0 转换为 1 时(接收到标志信号),随着加法进位位的传播,加法链的输出逐位由全 1 变为 0,形成非温度计编码形式<sup>[21]</sup>。加法链的输出经两级触发器锁存并传输进边缘检测模块。边缘检测使用多位与非门逻辑,将传入的非温度计编码转换为独热码,并进一步与编码器连接。编码器根据胖树原理搭建<sup>[22]</sup>,将独热码转换为表示进位信号传播到达位置的二进制数据。通过累加经过的所有延迟单元的延迟时间,可以得到待测  $\Delta t_1$  和  $\Delta t_2$  的具体数值。

在 FPGA 片上搭建校准模块,使用奇数个反相器建立环形振荡器来生成独立校准脉冲进行码密度测试,采集待校准延迟链各延迟单元在不同温度下的延迟时间数值。片上校准模块构建了一个三态状态机,状态转换如图 3 所示。其中,S0 为初始状态,当校准触发信号到来时进入 S1 状态。在 S1 状态下,存储模块中存储的所有校准数据清零,然后发送触发信号进入 S2 状态。在 S2 状态下,当随机脉冲沿着延迟链最终到达某个延迟单元时,将延迟链中该单元位置(上述编码器得到的位置)对应地址的 ram 表中数据加 1,建立统计直方图。

图 3 码密度校准状态机

Fig. 3 The state machine of code density calibration

依据搭建的统计直方图, 当输入测试信号数 N 足够大时, 可以计算出每个延迟单元的延迟时间:

$$t_i = T_{\text{elk}} \frac{N_i}{N} \tag{3}$$

其中, $T_i$ 为第i个延迟单元的延迟时间, $T_{elk}$ 为系统时钟周期(略小于延迟链总延迟时间,确保 TDC 测量范围的全覆盖), $N_i$ 为第i个延迟单元的跳变次数,N为跳变的总次数。

随机测试脉冲到达第 i 个延迟单元所用的累计延迟时间  $t_i$  为:

$$\begin{cases} t_0 = \frac{T_0}{2}, \\ t_i = \sum_{k=0}^{i-1} T_k + \frac{T_i}{2} & i > 0 \end{cases}$$

(4)

其中, $T_i$  为第 i 个延迟单元的延迟时间, $t_i$  为脉冲到达第 i 个延迟单元的总延迟时间。

实验中,片上校准模块测试信号数 N 被设置大于 5 100 000,将片上校准模块得到的统计直方图传输至上 位机,进而可以计算得到每个延迟单元的延迟时间数据

作为校准网络的训练样本。在构建 TDL-TDC 的过程中,需要特别注意布局布线位置,减少因跨越时域等原因导致的过大传播延迟。

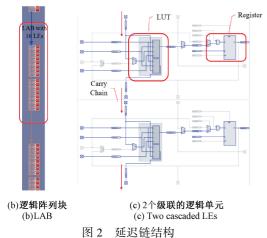

# 2 网络校准原理和结构

片上校准模块测量出不同温度条件下 128 个延迟单元的大量延迟时间数据,通过串口通信模块传输到上位机,基于网络校准的 FPGA-TDL-TDC 结构如图 4 所示。使用 MLP 神经网络训练每个延迟单元延迟时间与运行温度之间的函数关系,构建网络校准模块。实际工作中,通过采集当前运行温度数值送入训练完成的神经网络,可以独立得到各温度条件下延迟链 128 个延迟单元的不同延迟时间数据。本实验使用了两种不同 FPGA 芯片(ep4ce30f23c8 和 ep4ce115f23i7)验证方法的可行性。

图 4 网络校准的 FPGA-TDL-TDC 结构

Fig. 4 The structure of FPGA-TDL-TDC with network calibration

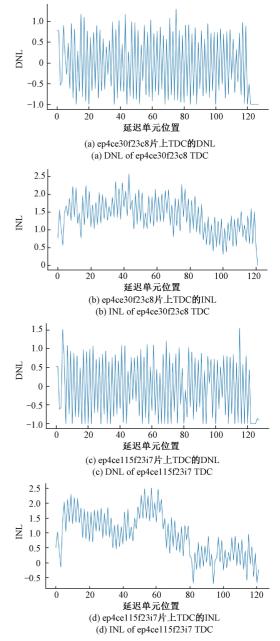

### 2.1 网络校准模块

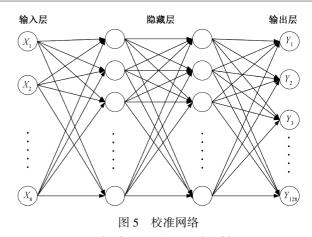

在上位机构建 4 层 MLP,以温度信息作为输入,输入 节点数设置为 8,可以输入商用 FPGA 芯片正常工作范围 内的所有温度信息,设置两层隐藏层,设置输出节点数为 128,作为 128 个不同延迟单元的延迟时间输出。网络结 构如图 5 所示。

网络训练参数包括: 网络输入值(温度) X, 期望输出量t, 网络输出值 Y 和期望输出 t 之间的偏差 e。通过调整输入层与隐藏层间的权重  $W_{ij}$ , 隐藏层与输出层间的权重  $T_{jk}$  以及网络的阈值,使误差沿着梯度下降的路径减少。在经过持续的迭代学习与训练后,一旦确定了与最小误差(误差设定为小于  $2\exp(-5)$ ) 相匹配的网络参数(包括权重和偏置),训练即告停止。通过学习训练的网络结构可以自主地对同类型的输入数据进行处理,输出经过非线性拟合且具有最小误差的结果。神经网络的权值更新步骤为:

Fig. 5 The diagram of network calibration

- 1) 初始化各层连接权值和偏置,设置学习率。

- 2)输入一组样本数据,处理计算各个节点的输出 数值。

- 3)根据梯度下降策略,以目标函数的负梯度方向对 参数进行调整。

标准神经网络算法,每次仅针对一个训练样例更新连接权,参数更新非常频繁,且对不同训练样例进行更新的效果可能会出现"抵消"的现象。为了最终在所有训练数据上均达到最小误差,采用累计误差来更新权值,在读取整个训练集后,将训练集分批次输入网络,每个批次输入32组数据,再对参数进行更新,可大大加快训练速度,并且防止网络出现过拟合。

通过上述 MLP 网络学习温度改变时延迟单元的延迟时间变化趋势。使用时,给定当前的运行温度条件值,根据训练完成的网络结构得到的函数关系,可以直接计算出当前温度条件下,延迟链每位延迟单元的延迟时间。后续工作中,利用训练好的 MLP 结构代替 TDC 实际工作中所需的大量校准步骤。上位机将网络给出的每个单元的延迟时间数据与当前粗计数器时间结果和编码器给出的位置二进制数据相结合,计算出待测的未知时间间隔。

### 2.2 温度变化对延迟链的影响

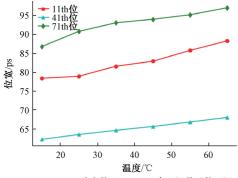

将搭建好带有 TDC 的 FPGA 放入温度可控的恒温箱中。通过从 15 ℃~65 ℃ 反复改变温度实验,每隔 10 ℃进行多次码密度测量,并将码密度结果传输作为训练样本,同时采集中间温度码密度结果用于网络精度测试,(详见第 3. 2 节)。从统计结果可以看出,随着温度的升高,延迟链不同位置的延迟时间变化趋势曲线不同,如图 6 所示。由于奇数位和偶数位延迟单元位宽的不一致性(进位链连接区域不同),与图 6 中延迟单元相邻的延迟单元位宽非常小。随着温度升高,各延迟单元的延迟时间逐渐增大,同时由于延迟链总延迟时间大于一个计数时钟周期,会导致延迟链终点位置的延迟单元逐渐未被使用。

- (a) ep4ce30f23c8片上第11、41、71个延迟单元的延迟时间

- (a) The delay time of 11th,41st, and 71st bins of ep4ce30f23c8  $\,$

- (b) ep4ce115f23i7片上第11、41、71个延迟单元的延迟时间

- (b) The delay time of 11th,41st,and 71st bins of ep4ce115f23i7

图 6 延迟链不同位置的延迟时间

Fig. 6 Delay time in different positions of delay line

# 3 实验分析

实验每隔  $10 \, \mathbb{C}$  采集码密度测试数据用作训练样本, 将训练完成的网络结构代入 FPGA-TDL-TDC 检验, 检测 网络校准的可行性和拟合变化曲线的准确度。

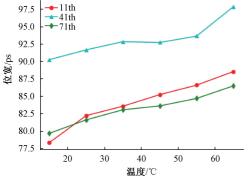

#### 3.1 TDC 测量

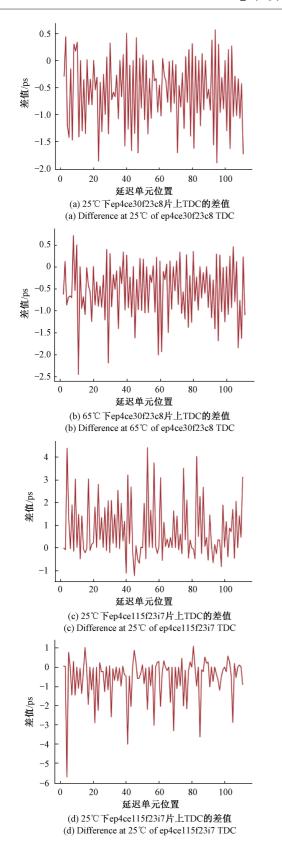

从图 6 中可以看到,由于各个延迟单元之间的差异,每个延迟单元延迟时间位宽的变化不一致。在 25 ℃下,测量并计算 ep4ce30f23c8 和 ep4ce115f23i7 两个芯片构建的 TDC 的微分非线性(differential nonlinearity, DNL)和积分非线性(integral nonlinearity, INL),如图 7 所示。在 25 ℃和 65 ℃下,基于两款芯片构建的 TDC 延迟链上128 个延迟单元延迟时间数据的网络校准结果和码密度校准结果之间差值如图 8 所示。

实验以 383. 351 445 ns 和 414. 523 066 ns 的固定时间间隔进行超过 8 200 次测量。实验得到在ep4ce30f23c8和 ep4ce115f23i7中构建的 TDC 分辨率分别为 56. 346 和 34. 115 ps。

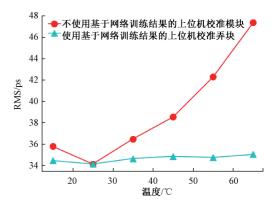

ep4ce115f23i7 中搭建的 TDC,有无使用网络校准模块补偿温度影响,在不同工作温度下测量的均方根(root

图 7 25 ℃下 TDC 的 DNL 和 INL Fig. 7 DNL and INL of TDC at 25 ℃

mean square, RMS) 结果对比如图 9 所示。其中, 码密度 测试数据在 25 ℃获得。

#### 3.2 网络校准模块的精度

进一步实验,将得到的网络校准结果数据拼接成曲线,使用 20 ℃、30 ℃、40 ℃、50 ℃、60 ℃(非训练温度)进行准确率测试。对通过上述网络搭建过程得到的延迟链的 128 个输出元素(128 个延迟单元的延迟时间),比较每个元素在不同温度的预测值与实测数据(码密度测量结果)的误差是否在给定范围内(1%以内)。如果在给定范围内,则标记为 1,否则标记为 0。将全 1 的数量

图 8 网络温度校准和码密度校准下 128 个延迟单元位宽差值

Fig. 8 Difference of bin width of 128 delay bins between network temperature calibration and code density calibration

图 9 使用和不使用网络校准模块在不同温度下 TDC 的 测量精度和均方根统计结果对比

Fig. 9 The resolution of TDC and comparison of root mean square(RMS) results at different temperatures with and without network calibration

除以总数 128。最终得到的网络准确率为 91%。

# 4 讨论

### 4.1 上位机网络校准

使用上位机的网络校准模块,通过搭建 MLP,能够建立起温度信息与延迟单元延迟时间之间的非线性关系。使用时,可以独立于其他工作模块获得延迟链中的每个单元的延迟时间数据,减少片上系统的死区时间。

从图 8 和 9 可以看出,利用网络校准模块进行温度校准,可以拟合 TDC 长延迟链上各延迟单元的延迟时间变化曲线,并补偿温度变化对延迟时间的影响,使得 TDC 在不同温度条件下有较好的适应性。

### 4.2 网络校准的通用性

实验表明,基于上位机的网络校准结构可以适用于不同的 FPGA 芯片。由于结构本身不包含 FPGA 相关信息,网络的训练样本中包含了不同芯片的特殊性。因此,只需要改变输入的训练数据,经过相同的计算过程,就可以得到另一块不同 FPGA 芯片上 TDC 的不同延迟时间。当需要适应更宽的温度范围或者添加更多的影响因素时,可以通过增加网络的输入节点数来学习特征值。

# 5 结 论

神经网络是一种高度并行的信息处理系统,具有很强的自适应学习能力,不依赖于研究对象的数学模型,对系统参数的变化和被测对象的外部干扰具有良好的鲁棒性。通常,当不同参数变化时,TDC 不同位置的延迟单元延迟时间变换关系的数学模型是复杂的。采用网络标定可以优化线性标定模式,在需要大量测量时减少人工工

[10]

作量,得到比人力推导数学模型更准确的拟合结果。每个延迟单元的数值由独立于片上系统的网络校准模块获得,从而减少了死区时间的产生。同时,获得数据可以存储在上位机中,以配合后续的计算处理需求,减少片上资源的占用。

基于上位机的网络校准结果易于移植,只需稍作调整即可适应不同的 FPGA 芯片和运行温度条件。利用网络学习复杂模型的方法,给出了学习和补偿复杂因素对TDC 影响的一种可能性。

### 参考文献

- [ 1 ] YOSHIOKA K, KUBOTA H, FUKUSHIMA T, et al. A 20-ch TDC/ADC hybrid architecture LiDAR SoC for 240× 96 pixel 200-m range imaging with smart accumulation technique and residue quantizing SAR ADC [ J ]. IEEE Journal of Solid-State Circuits, 2018, 53:3026-3038.

- [ 2 ] KERANEN P, KOSTAMOVAARA J. A wide range, 4. 2 ps(rms) precision CMOS TDC with cyclic Interpolators based on switched-frequency ring oscillators [ J ]. IEEE Transactions on Circuitsand Systems I Regular Papers, 2015, 62(12):2795-2805.

- [ 3 ] KERANEN P, KOSTAMOVAARA J. 256 x TDC array with cyclic interpolators based on calibration-free 2x time amplifier[J]. IEEE Transactions on Circuits and Systems I; Regular Papers, 2018, 66(2);524-533.

- [4] LIU C, WANG Y. A 128-Channel, 710 M samples/ second, and less than 10 ps RMS resolution time-todigital converter implemented in a Kintex-7 FPGA[J]. IEEE Transactions on Nuclear Science, 2015, 62(3): 773-783.

- [ 5 ] WON J, KWON S I, YOON H, et al. Dual-phase tapped-delay-line time-to-digital converter with on-the-fly calibration implemented in 40 nm FPGA [ J ]. IEEE Transactions on Biomedical Circuits and Systems, 2016, 10(1):231-242.

- [ 6 ] MATTADA M, GUHILOT H. Time-to-digital convertersa comprehensive review [ J ]. International Journal of Circuit Theory and Applications, 2021, 49:778-800.

- [7] DONG X, MA C, ZHAO X, et al. A high resolution multi-phase clock time-digital convertor implemented on Kintex-7 FPGA [J]. Journal of Instrumentation, 2020, 15(11): T11005.

- [8] KWIATKOWSKI P, SZPLET R. Efficient implementation of multiple time coding lines-based TDC in an FPGA device [J]. IEEE Transactions on Instrumentation and Measurement, 2020, 69 (10): 7353-7364.

[9] 李欢,余红英. 基于 FPGA 的高性能激光雷达测距系统设计[J]. 电子测量技术, 2021, 44(20):6-10. LI H, YU H Y. Design of high performance lidar ranging system based on FPGA [J]. Electronic Measurement Technology, 2021, 44(20):6-10.

汪玉传,梁华国,鲁迎春,等. 基于 STR 的两级差分的

- 高精度低功耗 TDC[J]. 电子测量与仪器学报, 2023, 37(6):136-146.

WANG Y CH, LIANG H G, LU Y CH, et al. STR-based two-stage differential high-precision and low-power TDC [J]. Journal of Electronic Measurement and Instrumentation, 2023, 37(6):136-146.

- [11] 卜朝晖,常仙云,陈文星,等. 基于可触发环形振荡器的高精度时间间隔测量[J]. 仪器仪表学报, 2019, 40(5):10-18.

BU ZH H, CHANG X Y, CHEN W X, et al. Highprecision time interval measurement based on triggerable ring oscillator [J]. Chinese Journal of Scientific Instrument, 2019, 40(5):10-18.

- [12] 郭围围,尹勇生,龚号,等. 基于时间放大技术的时间数字转换器的设计[J]. 电子测量与仪器学报, 2022, 36(4):98-105.

GUO W W, YIN Y SH, GONG H, et al. Design of time-to-digital converter based on time amplifier[J]. Journal of Electronic Measurement and Instrumentation, 2022, 36(4):98-105.

- [13] 刘音华,刘正阳,刘琼瑶,等. FPGA 进位链实现 TDC 的若干关键技术问题[J]. 电子测量技术, 2018, 41(14):122-127.

LIU Y H, LIU ZH Y, LIU Q Y, et al. The pivotal technical issue of TDC based on FPGA carry-chain[J]. Electronic Measurement Technology, 2018, 41(14): 122-127.

- [14] 李海涛,李斌康,田耕,等.一种通用的时间数字转换器码密度校准信号产生方法及其实现[J]. 电子与信息学报,2021,43(8):2121-2127.

LI H T, LI B K, TIAN G, et al. A general method of generating code density calibration signal for time-to-digital converter and its realization [J]. Journal of Electronics & Information Technology, 2021, 43(8): 2121-2127.

- [15] PAN W, GONG G, LI J. A 20-ps time-to-digital converter (TDC) implemented in field-programmable gate array (FPGA) with automatic temperature correction[J].

IEEE Transactions on Nuclear Science, 2014, 61: 1468-1473.

[18]

- [16] QIN X, WANG L, LIU D, et al. A 1.15-ps bin size and 3.5-ps single-shot precision time-to-digital converter with on-board offset correction in an FPGA [J]. IEEE Transactions on Nuclear Science, 2017,64: 2951-2957.

- [17] 甄国涌,苏慧思,陈建军,等. 基于 FPGA 的 PCIe 接口的数据传输设计与实现[J]. 国外电子测量技术, 2021, 40(12):72-76.

- ZHEN G Y, SU H S, CHEN J J, et al. Design and implementation of data transmission based on FPGA PCIe interface [ J ]. Foreign Electronic Measurement Technology, 2021, 40(12):72-76.

任勇峰,冯宇航,刘东海. 基于 FPGA 的多通道数字变

- 换器的设计与实现[J]. 国外电子测量技术, 2022, 41(4):176-180.

REN Y F, FENG Y H, LIU D H. Design and implementation of multi-channel digital converter based on FPGA [J]. Foreign Electronic Measurement Technology, 2022, 41(4):176-180.

- [19] WANG R, WANG T. Design of intelligent pension online monitoring system under the environment of internet of things[J]. Instrumentation, 2023, 10: 53-64.

- [20] KUANG W, LUO W. Based on STM32 of CNN speech keyword command recognition system[J]. Instrumentation, 2023, 10(1):17-22.

- [21] 庞高远,孟煦,郭围围,等. 新型两步式高精度 TDC 的设计[J]. 电子测量与仪器学报, 2021, 35(7): 115-122.

PANG GY, MENG X, GUO W W, et al. Design of a novel high precision TDC with two-step quantization[J]. Journal of Electronic Measurement and Instrumentation, 2021, 35(7):115-122.

- [22] SHEN Q, ZHAO L, LIU S B, et al. A fast improved fat tree encoder for wave union TDC in an FPGA [J]. Chinese Physics C, 2013, 37(10): 106102.

### 作者简介

许玥,2018年~2024年于中国科学技术大学纳米技术与纳米仿生学院(即中国科学院苏州纳米技术与纳米仿生研究所)攻读博士研究生,主要研究方向为数字电路设计与激光雷达系统集成。

E-mail: yxu2019@ sinano. ac. cn

Xu Yue studied as a doctoral student at the School of Nano-Tech and Nano-Bionics, University of Science and Technology of China (with the Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences), between 2018 and 2024. Her main research interests include digital circuit design and the integration of lidar systems.

吴东岷(通信作者),1997年于南京大学物理系获得学士学位,2000年于南京大学物理系获得硕士学位,2005年于美国加州大学洛杉矶分校机械与航空工程系获得博士学位。2006年~2007年于美国加州大学伯克利分校机械工程系担任博士后,现为

中国科学院苏州纳米技术与纳米仿生研究所研究员,上海科技大学特聘教授,主要研究方向为激光显示技术、MEMS 器件及加工技术、AFM 探针及硅悬梁传感器、生物成像技术等。

E-mail: dmwu2008@ sinano. ac. cn

Wu Dongmin (Corresponding author) received his B. Sc. degree from Nanjing University, Department of Physics in 1997, M. Sc. degree from Nanjing University, Department of Physics in 2000, and Ph. D. degree from University of California, Los Angeles (UCLA), Department of Mechanical and Aeronautical Engineering in 2005, respectively. 2006-2007, University of California, Berkeley (UCB), Department of mechanical engineering, postdoctoral fellow. Now he is a professor in Suzhou Institute of Nano-Tech and Nano-Bionics, Chinese Academy of Sciences, and the Shanghai Tech University. His main research interests include laser display technology, MEMS devices and processing technology, AFM probe and silicon cantilever sensor, biological imaging technology, etc.