Vol. 36 No. 9

DOI: 10. 13382/j. jemi. B2104965

# 用于 CZT 探测器前端的数字自校准 SAR-ADC 设计\*

刘 伟 郭尚尚 商世广

(西安邮电大学电子工程学院 西安 710121)

摘 要:为了满足碲锌镉(CZT)探测器前端读出系统对模数转换器(ADC)的特殊需求,设计实现了一款 12 bit 1.6 MS/s 的前台数字自校准逐次逼近型(SAR)ADC。采用先校准后正常输出的工作方式以提高数据转换的实时性,校准模式下,SAR-ADC 核心部分对差分斜坡输入电压注入低幅值扰动,再利用最小均方(LMS)自适应算法在数字域对亚二进制电容权重进行校准并固定;正常工作模式下,按照已经校准的权重值正常输出数字码。搭建数模混合仿真平台进行仿真验证,结果表明,当时钟信号频率为 20 MHz,输入信号频率为 239.1 kHz 时,校准后与校准前相比,SAR-ADC 的信噪失真比(signal-to-noise and distortion ratio, SNDR)由 45. 59 dB 提升到了 72. 35 dB,有效位数(effective number of bit, ENOB)由 7. 28 bit 提升到了 11. 73 bit,SAR-ADC 性能明显提升,前端读出电路与 SAR-ADC 的联合线性度  $\delta$  为-0.29%  $\sim$  0. 34%,能够满足 CZT 探测器前端读出系统的使用需求。

关键词:探测器;模数转换器;校准;最小均方(LMS)

中图分类号: TN453; TN432

文献标识码: A

国家标准学科分类代码: 510.3040

### Design of SAR-ADC with digital self-calibration for CZT detectors front-ends

Liu Wei Guo Shangshang Shang Shiguang

(School of Electronic Engineering, Xi'an University of Posts and Telecommunications, Xi'an 710121, China)

Abstract: In order to meet the special requirements of the front-end readout system of cadmium zine telluride (CZT) detector for analog to digital converter (ADC), a foreground digital self-calibration successive approximation register (SAR) ADC with 12 bit 1.6 MS/s is presented. The working mode of calibration followed by output is adopted to improve the real-time performance of data conversion. In the calibration mode, the core part of SAR-ADC injects low amplitude disturbance to the differential ramp input voltage, then uses the least mean square (LMS) adaptive algorithm to calibrate and fix the Sub-radix-2 capacitance weight in the digital domain. In the normal working mode, the digital code is output normally according to the calibrated weight value. A digital-analog hybrid simulation platform is built for simulation and verification. The results show that when the clock signal frequency is 20 MHz and the input signal frequency is 239.1 kHz, the signal-to-noise and distortion ratio (SNDR) of SAR-ADC after calibration is increased from 45.59 dB to 72.35 dB, and the effective number of bit (ENOB) is increased from 7.28 bit to 11.73 bit. The performance of SAR-ADC is obviously improved, and the linearity  $\delta$  between front-end readout circuit and SAR-ADC is  $-0.29\% \sim 0.34\%$ , which can meet the requirements of CZT detector front-end readout system.

Keywords: detector; analog-to-digital converter; calibration; least mean square (LMS)

### 0 引 言

碲锌镉(cadmium zine telluride, CZT)探测器是核辐射探测器的典型代表,已广泛应用于医学成像、核安全监

测和空间探测等领域<sup>[1-2]</sup>,在 CZT 探测器中,探测器元件 探测到的电信号非常微弱,为了提高监测灵敏度,就需要 高性能的前端读出系统,模数转换器 (analog-to-digital converter, ADC)作为 CZT 探测器前端读出系统的关键模 块,因此对其转换精度、面积及功耗就具有严格的 要求[3-6]。

逐次逼近型(successive approximation register, SAR) ADC 结构简单,特别适合小面积及低功耗的应用场 景[7],已经成为用于 CZT 探测器前端 ADC 的研究热点。 然而,SAR-ADC 的设计还存在诸多挑战,研究发现,高性 能 SAR-ADC 受限于电容权重失配、比较器偏移和噪声等 非线性因素的影响,其中电容权重失配对 SAR-ADC 的转 换精度影响最大,往往会将 SAR-ADC 的分辨率限制在 10 bit 以下[8-9]。为了减小电容失配对 SAR-ADC 转换精 度的影响,设计者通过增大电容尺寸来提高匹配性,但这 会增大芯片的功耗和面积,并且降低 ADC 转换速率[10], 另一种有效的措施是采用校准技术对电容权重进行校 准[11-13],数字校准方法相对于模拟校准,校准精度更高、 速度更快[14-16],因此数字校准技术已经成为 SAR-ADC 校 准的研究热点。目前比较流行的方法是通过注入低幅值 扰动[16-17]或伪随机序列[18],利用自适应滤波算法在数字 域调整 ADC 的输出,从而在后台实现对 ADC 的数字校 准,文献[16]基于线性叠加原理,对同一个模拟量注入 正负扰动,在数字域利用最小均方(least mean square, LMS)算法对电容权重实现校准;文献[18]将伪随机序列 (pseudo-noise, PN)注入到 ADC 中,从而在数字域补偿 失配误差,以上校准方法的不足之处在于 SAR-ADC 正常 工作时,校准算法会进行大量的重复性迭代,致使数据传

输的实时性不强,进而影响 SAR-ADC 的转换速率。

针对以上问题,本文拟提出一种前台数字自校准 SAR-ADC,通过先校准后正常输出的工作方式,将后台校准转移到前台,电路校准阶段,对斜坡信号产生模块输出的模拟电压  $V_{\rm IN}$  分别加入  $\pm \Delta a$  的扰动,依次量化后得到权重误差,再利用 LMS 算法对亚二进制电容权重进行迭代训练;在经过一定次数的迭代训练之后,校准控制信号控制 SAR-ADC 系统进入正常工作模式,电路会根据已经校准的权重值输出正确的数字码。所设计的前台数字自校准 SAR-ADC 校准阶段不需要任何外部信号,相对于数字后台校准,数据传输实时性强,校准算法不再影响 ADC的转换速率。

## 1 数字自校准 SAR-ADC 结构及校准算法 原理

#### 1.1 整体结构

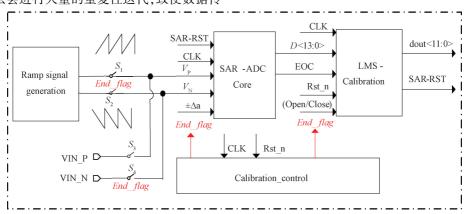

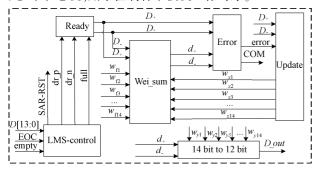

本文提出的前台数字自校准 SAR-ADC 整体框图如图 1 所示,其包括 4 个部分,分别是斜坡信号产生电路 (ramp signal generation)、SAR-ADC 核心电路(SAR-ADC core)、LMS 数字校准电路(LMS calibration)以及校准控制电路(calibration-control)。

图 1 数字自校准 SAR-ADC 整体框图

Fig. 1 Digital self-calibration SAR-ADC

电路刚上电时,SAR-ADC 工作在校准模式( $M_0$ )下,此时斜坡信号产生电路产生差分输入电压  $V_P$ 、 $V_N$ ,其经过 SAR-ADC 核心部分会加入± $\Delta a$  的抖动,然后依次量化得到数字码  $D_+$ 和  $D_-$ ,当转换结束信号 EOC 有效时,LMS数字校准电路会依次读入  $D_+$ 、 $D_-$ ,对权重进行迭代校准,该组数字码读入完成后,LMS 数字校准电路产生 SAR-RST 信号控制 SAR-ADC 核心电路进行下一次采样。在经过一定次数的迭代训练之后,所有的权重值都会趋于最佳值,此时校准控制电路(calibration-control)就会产生

一个校准结束信号  $End_flag$  去控制 SAR-ADC 核心部分 (SAR-ADC core),使其不加入抖动,同时也会控制 LMS 数字校准电路 (LMS-calibration) 不再校准,整个 SAR-ADC 电路将工作在正常模式( $M_1$ )下,电路会根据已经校准的权重输出正确的数字码,当下一次电路状态改变时,只需要改变复位信号  $Rst_n$  的值,就可以重新对权重进行迭代训练。

#### 1.2 基于扰动技术的 LMS 校准算法原理

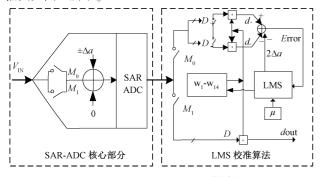

对于一个线性系统来说,在模拟域增加偏移量  $\pm \Delta a$

之后,能够在数字域被去除。SAR-ADC 的 LMS 校准技术 框图如图 2 所示。

图 2 SAR-ADC 的 LMS 校准技术框图

Fig. 2 LMS calibration technology of SAR-ADC

在校准模式( $M_0$ )下,对模拟输入电压  $V_{\text{IN}}$  分别加入  $\pm \Delta a$  的抖动,经过 SAR-ADC 核心部分会被转换为对应 的数字码  $D_+$ 和  $D_-$ ,其具有相同的初始权重,可以计算得到  $V_{\text{IN}}$   $\pm \Delta a$  的量化值  $d_+$ 、 $d_-$ :

$$d_{+} = \sum_{i=0}^{N-1} b_{i+} w_{i} + d_{os}$$

(1)

$$d_{-} = \sum_{i=0}^{N-1} b_{i-} w_{i} + d_{os}$$

(2)

$d_{\perp}$ - $d_{\perp}$ 与 2 $\Delta a$  作差就是权重误差 error:

$$error = d_{+} - d_{-} - 2\Delta a \tag{3}$$

error 的表达式又可以写为:

$$error = \sum_{i=0}^{N-1} (b_{i+} - b_{i-}) w_i - 2\Delta a$$

(4)

LMS 算法根据 error 的值,对每一位权重  $w_i$  进行迭代,使其趋近于最佳值,权重迭代式为:

$$w_{i}[n+1] = w_{i}[n] - \mu_{w}error[n](b_{+,i}[n] - b_{-,i}[n]) \quad i = 0,1,\cdots$$

$$(5)$$

$w_i$ 是  $b_i$ 位的权重, $\mu_w$ 是递归的步长,n为迭代次数。 当所有权重都被校准完成之后,SAR-ADC 核心部分和校 准部分会同时进入正常工作模式( $M_1$ ),SAR-ADC 核心 部分不会加入抖动,校准部分也不会工作,而电路记录了 最佳的权重值,此时 SAR-ADC 正常采样量化输出,每个 采样周期只输出一个数据。

# 2 具体电路实现

#### 2.1 斜坡信号产生电路

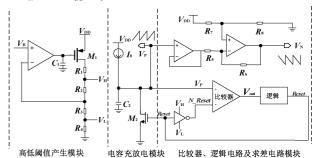

用于 SAR-ADC 前台数字校准的斜坡信号产生电路 如图 3 所示,此模块的主要作用是在校准阶段产生差分的输入信号  $V_P$ 、 $V_N$ ,因此整个 SAR-ADC 系统校准阶段不需要任何外部输入,可实现自校准。斜坡信号产生电路由电容充放电模块、比较器模块、逻辑模块、求差电路模块以及高低阈值产生模块共同构成。

电路刚上电时,Reset 信号为低电平,则反相器输出  $N_Rest$  为高电平,其值为  $V_H$ ,同时  $M_2$  管工作在截止状态,电流源对电容  $C_2$  进行充电,随着充电时间的增加,比较器正向端电压  $V_P$  会逐渐升高,当  $V_P$  大于  $N_Rest$  时,比较器输出  $V_{out}$  变为高电平,经过逻辑电路之后 Reset 也为高电平,反相器输出  $N_Rest$  变为低电平  $V_L$ ,同时  $M_2$  导通,电容放电,电压  $V_P$  随着放电时间的增加会逐渐减小,当  $V_P$  小于  $V_L$  时,比较器则会输出低电平,经过逻辑电路 Reset 也为低电平,此时  $M_2$  截止,电流源再次对电容进行充电。为了得到幅值相同方向相反的输入信号  $V_N$ ,还加入了一个求差电路,所选电阻满足  $R_6/R_5 = R_8/R_7 = 1$ ,则  $V_N$  等于  $V_{DD} - V_P$ 。

图 3 斜坡信号产生电路原理

Fig. 3 Ramp signal generating circuit schematic diagram

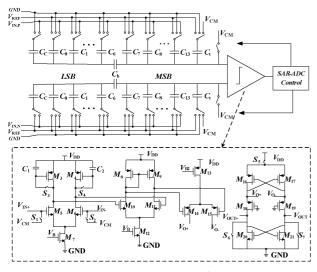

#### 2.2 SAR-ADC 核心电路实现

SAR-ADC 核心电路如图 4 所示,主要由电容阵列、比较器、逐次逼近控制模块共同构成。为了提高共模噪声抑制能力和转换精度,电容阵列采用差分结构,整个DAC 部分采用 1.86 进制、14 bit 的电容阵列组合而成,分数桥电容  $C_s$  的加入可以有效减少总电容的大小。为了实现基于扰动的数字校准,模拟偏移量通过电容  $C_t$  来注入, $C_t$  的大小等于单位电容  $C_0$ 。在采样阶段, $C_t$  复位到 GND,在两次转换阶段, $C_t$  根据扰动信号选择  $V_{REF}$  或 GND。当  $C_t$  选择  $V_{CM}$  时,校准功能无效。

为了实现高速、高精度的数据转换,本文采用一款失调电压自消除的高速比较器。结合前置放大器负指数响应与锁存器正指数响应的特点,采用三级级联的前置放大器使输入足够大,然后加到锁存器上,优化了比较器的速度。为了克服失调电压对比较器精度的影响,采用失调存储技术对失调电压进行存储后消除,将失调存储电容放在信号通路之外,减小了失调存储电容对比较器带宽和速度的影响。

#### 2.3 校准算法电路实现

SAR-ADC 校准电路通过 Verilog HDL 代码实现,其实现框图如图 5 所示,主要包括 LMS 控制模块(LMS control)、准备模块(Ready)、求权重和模块(Wi-Sum)、求权重误差模块(Error)、权重迭代模块(Update)以及最后

图 4 SAR-ADC 核心电路原理

Fig. 4 SAR-ADC core circuit schematic diagram

的 14 bit 转 12 bit 模块(14 bit to 12 bit), 电路实现中使用了多个状态机,用于控制各个模块工作时序。

图 5 校准算法实现框图

Fig. 5 Calibration algorithm implementation block diagram

当校准使能信号为高电平时,表示电路工作在校准模式,此时模拟输入电压  $V_{\rm IN}$  经过 SAR-ADC 核心部分就

会产生一个正抖动数据  $D_+$ 和一个负抖动数据  $D_-$ , EOC 信号有效时, LMS 控制模块(LMS-control)依次读入  $D_+$ 、 $D_-$ ,并保存在寄存器  $dr_-$ p 与  $dr_-$ n 中, 在保存之前, 对两个数字码比较大小, 确保  $dr_-$ p 的数据大于  $dr_-$ n。保存后向 ready 模块发送 full=1 的信号, 然后 ready 模块会将寄存器中的数据取出给其他模块进行校准。

求权重和模块设置相同的初始权重  $w_{ji}$ ,每位权重均为 23 bit 二进制数,其中低 10 bit 为小数部分,高 13 bit 为整数部分,此模块负责将数字码与初始权重进行加权求和,从而得到加权和  $d_+$ 、 $d_-$ ,然后求权重误差模块(Error)会根据输入的  $d_+$ 、 $d_-$ 得到权重误差 error,紧接着权重迭代模块(Update)根据 error 的值对权重进行迭代,迭代完成后,新得到的权重  $w_{xi}$  会再一次返回到求权重和模块(Wi-sum)进行加权求和。由于电容失配具有不确定性,因此 error 的值也无法确定,若以误差值作为结束校准的条件,当权重误差过大时,可能会导致校准不能收敛,因此,在实际电路中,通过设定校准的次数作为校准结束的条件,当达到设定的校准次数时,14 bit 转 12 bit 模块就会用最终的权重值  $w_{yi}$  将 14 bit 数字码压缩为12 bit 二进制数字码进行输出。

### 3 电路仿真与结果分析

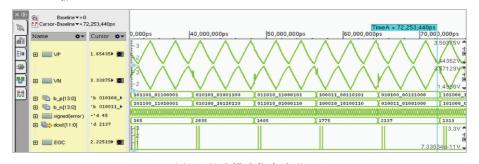

基于 TSMC 0.35  $\mu$ m 2P4M CMOS 工艺,对本文所设计的 SAR-ADC 进行数模混合仿真验证。图 6 所示为校准模式仿真波形,其中, $V_P$ 、 $V_N$  分别表示斜坡信号产生电路产生的差分输入信号; $b_P$  和  $b_n$  分别表示加入正负抖动之后的 14 bit 数字码;error 表示权重误差;dout 表示压缩成 12 bit 的数字码;EOC 为转换结束信号,从图 6 中可以看出,当转换结束信号 EOC 信号有效时,校准电路依次读入  $b_p$  和  $b_n$ ,然后数字电路会根据设定的校准次数作为终止的条件对权重进行校准。

图 6 校准模式仿真波形

Fig. 6 Calibration mode simulation waveform

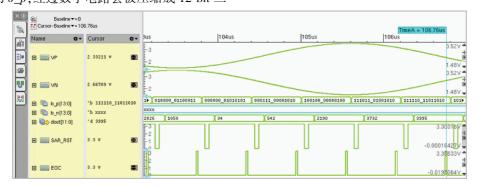

迭代训练之后,所有的权重值都会趋于最佳值,此时校准控制电路(calibration-control)会产生一个校准结束

信号 End\_flag 去控制 SAR-ADC 核心部分 (SAR-ADC core),使其不加入抖动,同时也会控制 LMS 数字校准电

路 (LMS-calibration)不再校准,SAR-ADC 正常工作阶段的仿真波形如图 7 所示,从图中可以看出,SAR-ADC 只输出一个数字码  $b_p$ ,经过数字电路会被压缩成 12 bit 二

进制数字码进行输出,这个数字码就是校准之后正确的数字码。

图 7 正常工作模式仿真波形

Fig. 7 Normal working mode Simulation waveform

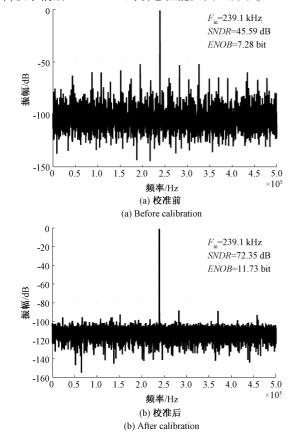

设定模拟电路电源电压  $V_{\rm DD}$  = 5 V,参考电压  $V_{\rm REF}$  = 4.096 V,时钟信号频率为 20 MHz,占空比为 50%,输入幅度为 2.048 V、频率为 239.1 kHz 的差分正弦波,然后对 ADC 的输出进行采样,对采样得到的数据进行 FFT 分析,校准前后 SAR-ADC 的动态性能如图 8 所示。

图 8 SAR-ADC 校准前后动态性能对比 Fig. 8 Dynamic performance comparison of SAR-ADC before and after calibration

由图 8 (a)可以看出,校准前 SAR-ADC 的信噪失真比(SNDR)为 45.59 dB,有效位数(ENOB)为 7.28 bit,通过校准算法校准之后的频谱图如图 8 (b)所示,SNDR 提升到了 72.35 dB,ENOB 提升到了 11.73 bit。校准算法效果明显,SAR-ADC 动态性能显著提升。

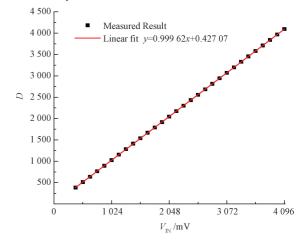

为了测试前端读出电路与本文所设计 SAR-ADC 的联合线性度  $\delta$ ,输入以 128 mV 线性增加,范围为 384~4 096 mV 的模拟电压  $V_{\rm IN}$ ,对 SAR-ADC 输出进行仿真,仿真结果如图 9 所示,可以看到,对应的数字码从 384 线性增加到 4 096。对得到的数据点进行线性拟合,得到的拟合曲线为 y=0.999 62x+0.427 07。

图 9  $V_{\rm IN}$ 与 D 的对应关系

Fig. 9 Correspondence between  $V_{\text{IN}}$  and D

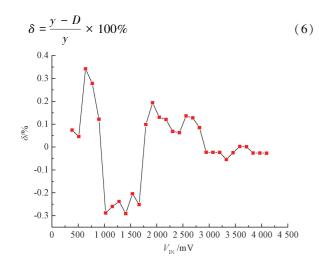

联合线性度  $\delta$  的定义式如式( $\delta$ )所示,计算得到  $\delta$  与输入电压  $V_{\text{IN}}$  的对应关系如图 10 所示,可以看出, $\delta$  的范围为 - 0. 29%  $\sim$  0. 34%, SAR-ADC 电路具有良好的线性度。

图 10  $V_{\text{IN}}$ 与 $\delta$ 的对应关系

Fig. 10 Correspondence between  $V_{\text{IN}}$  and  $\delta$

SAR-ADC 校准前、后的动态性能参数如表 1 所示,对比可知,校准后 SAR-ADC 动态性能得到了明显提升。

表 1 SAR-ADC 校准前后的性能参数

Table 1 The performance parameters

before and after calibration

| 状态       | 校准前    | 校准前    |

|----------|--------|--------|

| SNDR/dB  | 45. 59 | 72. 35 |

| ENOB/bit | 7. 28  | 11. 73 |

本文所设计的 SAR-ADC 与其他文献对比结果如表 2 所示,可以看出,本文提出的 SAR-ADC 具有较好的有效位数(ENOB)和信噪失真比(SNDR),满足 CZT 探测器对高精度 SAR-ADC 的需求。

表 2 本文 SAR-ADC 和其他文献的性能对比 Table 2 The performance comparison between SAR-ADC proposed and others' work

| 指标                    | 文献[19] | 文献[20] | 文献[21]   | 本文       |

|-----------------------|--------|--------|----------|----------|

| 工艺                    | 110 nm | 110 nm | 0. 18 μm | 0. 35 μm |

| 速率/MS・s <sup>-1</sup> | 65     | 1      | 0. 2     | 1.6      |

| ENOB/bit              | 11. 19 | 11.5   | 11. 59   | 11.73    |

| $SNDR/\mathrm{dB}$    | -      | 71     | 71. 55   | 72. 35   |

### 4 结 论

本文设计实现了一款应用于 CZT 探测器前端的数字自校准 SAR-ADC。针对 SAR-ADC 电容失配影响转换精度及后台校准算法迭代复杂等问题,给出了解决方案,将后台校准对转换速率的影响转移到了前台。搭建了SAR-ADC 数模混合仿真验证系统对 ADC 进行了仿真验

证,结果表明,校准后 SAR-ADC 的信噪失真比(SNDR)由45.59 dB提升到了72.35 dB,有效位数(ENOB)由7.28 bit 提升到了11.73 bit,与前端读出前端电路联合线性度良好,适合CZT探测器前端读出系统的应用需求。

### 参考文献

[1] 傅楗强. 碲锌镉探测器若干关键技术研究[D]. 北京: 清华大学,2017. FU J Q. Research on the key techniques of CdZnTe

detector[D]. Beijing: Tsinghua University, 2017.

- [2] 刘凤琳. 一种应用于 CZT 像素阵列的核辐射探测器读出电路的研究[D]. 重庆:重庆大学,2012.

LIU F L. A study of a readout circuit used for CZT pixel arrays nuclear radiation detector [D]. Chongqing: Chongqing University,2012.

- [ 3 ] YIZHEN Z, JUEPING C, XINYU L, et al. A 3.66 μW 12 bit 1MS/s SAR ADC with mismatch and offset foreground calibration [ J ]. Microelectronics Journal, 2021, 116; 105244.

- [ 4 ] ZHENG Q, YUDONG O, LIJIE Y, et al. A 1 GS/s 10bit SAR ADC with background calibration in 28 nm CMOS [ J ]. Microelectronics Journal, 2021, 114:105120.

- [5] 佟星元, 位康康. 高速逐次逼近模/数转换器结构设计综述 [J]. 西安邮电大学学报, 2016, 21(2): 77-81.

- TONG X Y, WEI K K. Overview of the high-speed SAR ADC architecture design [J]. Journal of Xi'an University of Posts and Telecommunications, 2016, 21(2); 77-81.

- [6] CHU H, LI F. A 14bit 320MS/s pipelined-SAR ADC based on multiplexing of dynamic amplifier [C]. Proceedings of 2017 IEEE 12th International Conference on ASIC. 2017;704-707.

- [7] XUR, LIUB, YUAN J. Digitally calibrated 768-KS/s 10-b minimum-size SAR ADC array with dithering [J]. IEEE Journal of Solid-State Circuits, 2012, 47(9): 2129-2140.

- [ 8 ] DING M, HARPE P, LIU Y H, et al. A 46 μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration [ J ]. IEEE Journal of Solid-State Circuits, 2017, 423-432.

- [ 9 ] LONG C, JI M, NAN S. Capacitor mismatch calibration for SAR ADCs based on comparator metastability detection [J]. IEEE, 2015, 2357-2360.

- [10] DENG H, HU Y, WANG L. An efficient background calibration technique for analog-to-digital converters based on neural network-ScienceDirect [J]. Integration, 2020, 74:63-70.

- [11] DAI P, ZHAO Y, SHENG Y, et al. A self-calibration

[13]

method for capacitance mismatch in SAR ADC with split-capacitor DAC [J]. Microelectronics Journal, 2015, 46(6): 431-438.

陈红梅,黄超,邓红辉,等. 带参考通道的时间交叉

- [12] KURAMOCHI Y, MATSUZAWA A, KAWABATA M. A 0.05 mm² 110 μW 10 b self-calibrating successive approximation ADC core in 0.18 μm CMOS[C]. IEEE Asian Solid-State Circuits Conference, 2007; 224-227.

- ADC 数字后台校准方法[J]. 电子测量与仪器学报, 2015,29(12):1739-1745.

CHEN H M, HUANG CH, DENG H H, et al. Background digital calibration method for time-interleaved ADC using a reference ADC[J]. Journal of Electronic Measurement and Instrumentation, 2015, 29 (12): 1739-1745.

- [14] DING X, HOFMANN K, ZHANG L, et al. Redundant double conversion based digital background calibration of SAR ADC with convergence acceleration and assistance [C]. 2018 25th International Conference "Mixed Design of Integrated Circuits and System" (MIXDES), 2018:192-197.

- [15] WANG G, KACANI F, CHIU Y. IRD digital background calibration of SAR ADC with coarse reference ADC acceleration [J]. Circuits and Systems II: Express Briefs Transactions on, 2014, 61(1): 11-15.

- [16] LIU W, HUANG P, CHIU Y. A 12 bit, 45 MS/s, 3 mW, redundant successive-approximation-register analog-to-digital converter with digital calibration [J]. IEEE Journal of Solid-State Circuits, 2011, 46 (11): 2661-2672.

- [17] 黄继伟, 康健. 一种基于扰动的 SAR ADC 数字校准 算法 [J]. 微电子学, 2019, 49(5): 708-712.

HUANG J W, KANG J. A perturbation-based digital calibration algorithm for SAR ADC [ J ].

Microelectronics, 2019, 49(5): 708-712.

- [18] PENG X, FU T, BAO Q, et al. A new capacitor mismatch calibration technique for SAR ADCs[C]. 2018

14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2018;1-4.

- [19] SALVO A D. Design of a 12 bit SAR ADC with digital self-calibration for radiation detectors front-ends [C]. 2019 15th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), 2019: 125-128.

- [20] 徐亮,代志双,谢亮,等. 一种 12 位 1 MS/s 数字自校准 SAR ADC[J]. 微电子学,2019,49(3):320-325.

XU L, DAI ZH SH, XIE L, et al. A 12 bit 1 MS/s SAR ADC with digital self-calibration[J]. Microelectronics, 2019,49(3):320-325.

- [21] ZHANG X, WANG M, GUO L, et al. A 12 bit 200 KS/s SAR ADC with digital self-calibration [C]. 2017 IEEE 2nd Advanced Information Technology, Electronic and Automation Control Conference (IAEAC). IEEE, 2017; 2531-2535.

#### 作者简介

刘伟,2005年于西安理工大学获得学士学位,2008年于西安理工大学获得硕士学位,2017年于西北工业大学获得博士学位,现为西安邮电大学讲师,主要研究方向为模拟集成电路设计。

E-mail: liuweixu@ xupt. edu. cn

Liu Wei received his B. Sc. degree from Xi'an University of Technology in 2005, M. Sc. degree from Xi' an University of Technology in 2008, and Ph. D. degree from Northwestern Polytechnical University in 2017. Now he is a lecturer at Xi'an University of Posts and Telecommunications. His main research interest includes analog integrated circuit design.

**郭尚尚**(通信作者),2019年于兰州理 工大学获得学士学位,现为西安邮电大学硕 士研究生,主要研究方向为模拟集成电路 设计。

E-mail: LUT\_GS@ 163. com

**Guo Shangshang** (Corresponding author)

received his B. Sc. degree from Lanzhou University of Technology in 2019. Now he is a M. Sc. candidate at Xi'an University of Posts and Telecommunications. His main research interest includes analog integrated circuit design.