DOI: 10. 13382/j. jemi. B2104752

# 高集成度多种格式并行输出的视频测试信号源研制\*

马家麟<sup>1</sup> 孙海洲<sup>1</sup> 任贵珊<sup>1</sup> 王素珍<sup>1</sup> 邹开元<sup>2</sup> 王怀铭<sup>1</sup> (1.青岛大学电子信息学院 青岛 266071:2.海信智动精工有限公司 青岛 266520)

摘 要:在大规模自动化生产过程中,为了对不同型号的电视机主板进行测试,需要一种能同时输出不同格式、多种接口、多种分辨率的视频测试信号源。通过对多媒体视频传输原理及不同格式视频接口信号的研究,在一片先进的 Artix-7 系大规模可编程 XC7A100T 芯片上,实现了超高清、高清的数字视频 HDMI 接口信号和模拟标清视频 VGA、CVBS、YPRPB 格式的信号同时输出。首先,根据视频显示的基本原理,产生对应不同分辨率、不同场频的并行数字视频基带信号。然后,将并行的超高清、高清分辨率的数字视频信号进行并串转化,成为串行的 TMDS 信号,送到 HDMI 接口显示;将并行标清分辨率的信号送入调制模块及数模转换转器成为 CVBS、VGA、YPRPB 格式的模拟视频信号。在一片 XC7A100T 芯片内将并行的超高清、高清数字信号转换成串行差分 TMDS 信号,节省了视频信号的并串转换处理芯片,节约了成本。整个系统提高了产生视频测试信号的集成度,减小了测试装备的体积,方便生产视频设备的厂家进行测试。

关键词:图像分辨率;超高清/高清视频信号;视频信号接口;FPGA;TMDS信号

中图分类号: TN919.81;TP391 文献标识码:

文献标识码: A 国家标准学科分类代码: 510.10

# Implementation of the high-integration video signal-source with the multi-format and parallel-output function

Ma Jialin<sup>1</sup> Sun Haizhou<sup>1</sup> Ren Guishan<sup>1</sup> Wang Suzhen<sup>1</sup> Zou Kaiyuan<sup>2</sup> Wang Huaiming<sup>1</sup>

(1. School of Electronics & Information, Qingdao University, Qingdao 266071, China;

2. Hisense Smart Precision Co., Ltd., Qingdao 266520, China)

Abstract: In the large-scale automatic production process, in order to test different types of TV motherboards, it is very necessary that video test sources can output different formats, multi-interfaces and multi-resolution in parallel. Through the exploration of multimedia video transmission principle and video signal interface formats, the video test signal source is designed and realized in an advanced Artix-7 series large-scale programmable XC7A100T chip, which can output both ultra-high-definition and high-definition video HDMI interface signal, and analog standard definition video signal in VGA, CVBS and YPRPB format. First of all, parallel digital baseband video signals with different resolutions and field frequencies are generated according to the principle of video display. Then, the parallel ultra-high-definition and high-definition digital video signals are converted into serial TMDS signals in order to be sent to the HDMI interface for display; and the parallel standard resolution signal is sent to the modulation module and digital-to-analog converter to become analog video signal in VGA, CVBS and YPRPB format. In particular, the parallel ultra-high-definition and high-definition digital video signals are converted into serial TMDS differential signal inside the XC7A100T chip, which saves the video parallel-serial processing chips and reduces the cost of equipment. The whole system improves the integration level of video test signal, reduces the volume of test equipment, and the manufacturers of video equipment can be more convenient to test.

Keywords: image resolution; ultra/high-definition video signals; video signal Interface; FPGA; TMDS signal

#### 0 引言

随着显示技术的发展,出现了不同格式的显示屏,为 了驱动不同的显示屏,需要不同接口格式的视频处理主 板[1-5]。为了对不同视频主板同时测试,需要一种能并行 输出多格式、多种分辨率的视频测试信号源[6-8]。目前, 产生和处理不同格式的视频信号,通常组合多片可编程 逻辑器件 FPGA、DSP 和单片机 CPU 芯片来实现。有些 方式还附加了数据存储芯片 RAM,将视频数据存储到 RAM 中,通过读写 RAM 中的数据输出特定格式的视频 信号[10-12]。文献[9-11]使用 FPGA 器件将摄像头的数据 存储到 FPGA 内部的缓冲器中,经过不同编码输出不同 格式的视频信号送给下游器件。文献[12]用单片机芯 片实现视频处理,需要附加数据存储芯片 RAM,将视频 数据存储到 RAM 中,通过单片机对 RAM 中的数据进行 读写控制来输出视频信号。CN104125453A 专利公布了 一种多功能的测试信号发生分配器,提供一种综合测试 方案。每个模块使用一片 FPGA 器件实现,做成不同接 口的模拟、数字视频模块,在使用时根据需要可自由组 合。在测试时需要工位人员根据视频主板的不同进行更 换和组装,不利于提高效率。

随着高清、超高清信号的出现,要求视频信号源输出 HDMI 接口的信号,通常使用专用芯片将并行的视频信 号转换为串行的 HDMI 接口信号<sup>[13-15]</sup>,这样多路输出的 HDMI 接口,就需要多个并转串的芯片,不利于节约 成本。

本文采用集成度高的 Artix-7 系的大规模可编程 XC7A100 T的 FPGA 芯片,实现了一种高集成度的多种 格式并行输出的视频测试信号源。该芯片具有丰富的逻 辑编程单元和供用户使用的 IO 口(有 484 个引脚),在一 个芯片上能同时并行输出多种格式视频测试信号。在设 计中,严格按照超高清、高清、标清的格式标准实现视频 测试信号:充分利用该 FPGA 内部的逻辑及存储资源,采 用乒乓存取方法来处理像素数据[16-19]。采用 ARM 系列 的 STM32F407ZGT6 芯片向 FPGA 发送指令,控制系统工 作[20-21]。本视频信号源将多种格式的视频接口信号,如 超高清、高清数字视频(2 160×3 840、1 080×1 920、 1 366×768、1 280×768、1 280×720)的 HDMI 接口信号和 模拟标清视频接口信号 VGA、CVBS、YPRPB、DVI 在一个 大规模可编程 XC7A100 T 芯片上生成:同时在芯片内将 并行的超高清、高清数字信号转换成串行差分 TMDS 信 号,节省了视频信号并串转换处理芯片,提高了产生视频 测试信号的集成度,方便生产测试。

### 1 系统组成结构

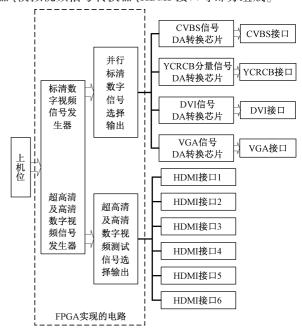

高集成度的多种格式并行输出的视频测试信号源的结构如图 1 所示。系统包括:上位机、超高清、高清数字信号视频源发生器、数字标清视频信号发生器、信号选择器、模拟视频信号转换器、HDMI接口等部分组成。

图 1 高集成度多种格式并行输出视频测试信号源的结构

Fig. 1 Structure for high-integration video signal-source with the multi-format and parallel-output

在 FPGA 内部产生不同格式和分辨率的超高清、高清及标清等数字视频信号,经过选择分配后,送到不同的视频接口,输出指令要求的视频测试信号;晶振电路把时钟信号处理后,为各级电路提供工作时钟。

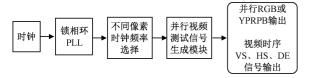

# 2 并行视频信号产生方法

信号源要求输出超高清、高清 HDMI 接口和模拟标清接口的测试信号,两种类型的信号都需要先在 FPGA 内部产生对应不同分辨率的数字信号,通过后续电路处理成指令要求接口的信号。FPGA 芯片内部产生并行视频信号的结构如图 2 所示,由时钟、锁相环、不同分辨率像素时钟信号选择、并行视频信号产生等模块组成。晶振时钟信号为 200 MHz,送到 FPGA 内部的锁相环 PLL,产生不同像素频率时钟信号,经过选择器,输出指令要求分辨率视频的像素时钟信号;在像素时钟信号作用下,产生并行视频 RGB 信号或 YCrCb 数据信号,以及视频时序控制的场同步 VS、行同步 HS、消隐 DE 等信号。不同分

辨率的并行数字视频信号的主要参数如表 1 所示。其中超高清分辨率为 3 840×2 160p, 场频分别是 60 和 30 Hz; 高清分辨率为 1 920×1 080p、1 920×1 080i、1 366×768p、1 280×720p、720×576p等;标清分辨率为 720×576i、720×480i等。

图 2 芯片内部产生并行视频信号的结构

Fig. 2 Structure of parallel video signal based on FPGA

表 1 常见分辨率对应的时钟参数

Table 1 Correspond to parameters for primary resolutions

| 分辨率                 | 场频/Hz | 行频/kHz  | 时钟/MHz |

|---------------------|-------|---------|--------|

| 3 840×2 160P@ 60 Hz | 60    | 135     | 594    |

| 3 840×2 160P@ 30 Hz | 30    | 67. 5   | 297    |

| 1 920×1 080P@ 60 Hz | 60    | 67. 5   | 148. 5 |

| 1 920×1 080i@ 60 Hz | 60    | 37. 125 | 74. 25 |

| 1 366×768P          | 60    | 47. 7   | 85     |

| 1 280×720P          | 60    | 45      | 74. 25 |

| 720×576p            | 50    | 31. 25  | 27     |

| 720×576i            | 50    | 15. 625 | 13. 5  |

| 720×480i            | 60    | 15. 75  | 13. 5  |

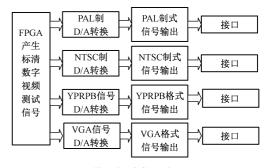

# 3 标清模拟接口测试信号产生方法

模拟标清信号产生结构如图 3 所示。CVBS 视频信号的产生方法是:由 FPGA 芯片内部产生并行的分辨率为 720×576i 及 720×480i 的 PAL、NTSC 制式的信号,送到对应 AV(CVBS)的视频 D/A 转换芯片,输出相应的CVBS 的视频复合信号;YPRPB 由 FPGA 芯片内部产生相应分辨率的彩色分量信号,送到相应的视频 D/A 转换芯片,输出信号到分量接口;VGA 视频信号是由 FPGA 芯片内部产生相应分辨率的 RGB 并行视频信号,送到VGA 模拟信号转换芯片,得到模拟 VGA 视频信号。总之,经过对应的数字转模拟芯片的变换,将并行数字信号转换成模拟信号,送到相应的接口上显示模拟测试信号。

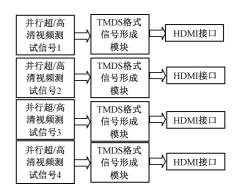

# 4 数字超高清、高清信号产生方法

数字超高清、高清 TMDS 格式信号产生结构如图 4 所示,由并行超高清、高清视频测试信号模块,TMDS 格式信号形成模块等两部分组成。并行超高清、高清视频测试信号模块的功能是在 FPGA 芯片内部产生不同分辨率的超高清、高清并行数字视频(3 840×2 160p、1 080×

图 3 模拟标清信号产生原理

Fig. 3 Analog SD signal generation

1920p、1366×768p、1280×720p、720×576p)信号,并行信号产生方法与图2所示的结构相同;此处并行RGB或YCrCb数据以及视频控制信号的场同步VS、行同步HS、消隐DE等信号对应是超高清及高清的视频信号参数。

图 4 数字超高清、高清 TMDS 格式信号产生方法

Fig. 4 Ultra HD and HD TMDS signal generation method

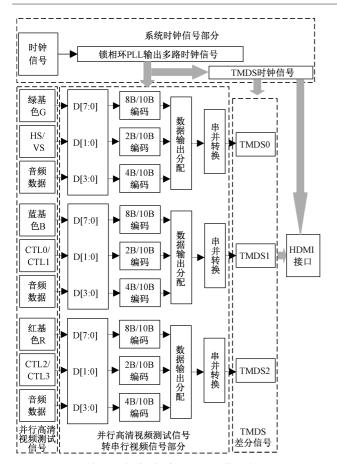

并行超高清、高清视频测试信号转换成串行 TMDS 格式信号的结构如图 5 所示,由系统时钟信号部分,并行超高清、高清视频测试信号输入、并行超高清、高清视频测试信号转串行视频信号、TMDS 差分信号形成等模块部分组成。

- 1) 系统时钟信号部分给电路的各模块提供工作时钟。将电路板上 200 MHz 的差分晶振时钟信号送到FPGA 芯片内部时钟管理系统的锁相环单元 PLL 上,产生多路时钟信号;其中一路与像素时钟信号同频同相,经过单端信号转双端差分处理后,成为差分的 TMDS 时钟信号;其他路的时钟信号送到并行超高清、高清视频测试信号转串行视频信号电路部分中,给输入信号缓冲模块、8B/10B、2B/10B、4B/10B编码模块、数据输出分配模块、并串转换模块等提供时钟信号。

- 2)并行超高清、高清视频测试信号输入部分对并行输入的 RGB 或 YCrCb 数据以及视频控制信号场同步 VS、行同步 HS、消隐 DE 等信号进行打包,将 RGB 或 YCrCb 数据与行同步 HS、场同步 VS 控制信号和音频信号打包成 3 组数据,如图 5 输入信号部分所示。第 1 组

图 5 并行超高清、高清视频测试信号转换成 串行 TMDS 格式信号结构图

Fig. 5 Structure diagram about changing parallel Ultra-HD and HD video signals into serial TMDS signal

为绿基色 G、行同步 HS 和场同步 VS、音频数据组合;第 2 组为蓝基色 B、附加的控制信号 CTLO/CTL1 及音频数据组合;第 3 组为红基色 R、附加的控制信号 CTL2/CTL3 及音频数据组合。其中每组中的视频数据总线为 8 bit,控制信号总线为 2 bit,音频数据总线为 4 bit。3 种数据分别在不同的时段传输,在行正程、场正程的时间段(active pixels, active line)传输视频数据;在图像的消隐时间(DE)段传输数字音频、控制和同步信号数据。

- 3)并行超高清、高清视频测试信号转串行视频信号部分主要由输入信号缓冲模块、8B/10B、2B/10B、4B/10B编码模块、数据输出分配模块、串并转换模块、低压差分信号 TMDS 形成模块构成。具体方法如下:

- (1)视频数据传输。3组中并行 D[7:0]的8位三基色 RGB 或分量视频 YCrCb 数据经过缓冲器后送到8B/10B编码模块中,在编码时钟信号作用下进行8B/10B编码处理,把每条通道的8bit视频数据转化为10bit直流平衡编码数据,送到数据输出分配模块,在行、场正程的时间选择输出。

- (2) 音频数据或辅助数据传输。3 组中并行 D [3:0]的4 bit 的音频数据或辅助数据,经过缓冲器后送到4B/10B编码模块中,在编码时钟信号的作用下成为10 bit 信号,送到数据输出分配模块,被选择输出。

- (3)控制信号传输。第1组通道中的行HS、场VS同步信号和第2组通道中的CTL0、CTL1以及第3组通道中的CTL2、CTL3经过缓冲器后送到2B/10B编码模块中,成为10bit的直流平衡编码信号,用于接收端识别视频数据和音频数据。同样这10位数据信号送到数据输出分配模块,被选择输出。

- (4)数据输出分配。3个通道中的数据输出分配模块是对输入的视频数据、音频或辅助数据、控制数据进行选择输出。根据视频传输的时序关系,在视频传输的正程时段的选择视频数据输出;在行、场的消隐的时间段,选择音频、控制数据输出。

- (5) 串并转换。在每个像素时钟周期中,将输出的 10 位数据进行并串转换,然后将单端信号转换成双端差 分信号,成为 3 组差分的 TMDS0、TMDS1、TMDS2 信号,与差分的像素时钟信号同时送到 HDMI 接口,显示视频信号。

#### 5 系统实现与测试

高集成度的多种格式并行输出的视频测试信号源系统使用的 FPGA 为 Xilinx 公司工业级 ARTIX-7 系列的芯片 XC7A100 T-2FGG484I。具有高精度、低抖动的时钟信号产生及锁定能力;内置 FIFO 以及片上数据缓存的双口RAM;有高速的数据采集、传输、数字图像处理等能力;经试验测试满足本视频信号源系统要求。系统使用 Verilog HDL 语言实现多种分辨率的并行数字视频信号及信号接口格式的转换,在 Xilinx 公司的 VIVADO 开发环境下编译及测试程序。用 ARM 系列的 STM32F407ZGT6 芯片向 FPGA 发送输出信号指令,7 寸的电容触摸屏 LCD 显示控制指令,FPGA 内部按照指令产生不同格式和分辨率的标清及超高清、高清数字并行信号。

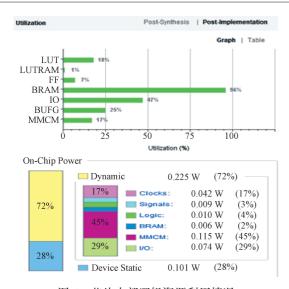

#### 5.1 芯片内部资源利用情况

系统使用的 VIVADO 开发工具可以实时观察芯片内部硬件电路布局及资源利用情况。图 6 是本视频信号源在芯片 XC7A100 T-2FGG484I 内部消耗的逻辑资源分布情况。从图 6 可见,存储单元 BRAM 资源使用最多,达到96%;占用了是 47%的 IO 口资源;缓冲单元 BUFG 占用22%;查找表 LUT 占用 18%;时钟管理资源 MMCM 占用17%。信号源系统在芯片 XC7A100 T-2FGG484I 内部过程总耗电是 0.356 W;其中,动态耗电 0.255 W,静态耗电 0.101 W.系统能够正常稳定的工作。

图 6 芯片内部逻辑资源利用情况

Fig. 6 Utilization of internal resources in FPGA chip

#### 5.2 系统测试

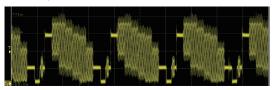

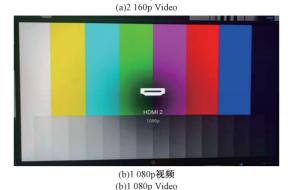

研制的视频测试信号源的输出信号有多种格式,即超高清、高清数字 HDMI 接口信号和模拟的 AV、分量YPRPB、VGA 信号。用示波器测试信号源输出几个典型的信号,如下面图所示。图 7 是 NTSC 制的 4 行 NTSC 制式信号,可以看到 4 行正程的视频彩条信号及行同步、色同步信号。图 8 是分量 YPRPB 格式的一个色差信号。图 9 是 1 080p 分辨率的高清 TMDS 差分信号的包络;图 10 是 1 080p 的 TMDS 信号的两场信号,场频是 60 Hz。图 11(a)、(b)是将信号源输出的超高清、高清视频信号输入到电视机主板后,显示屏显示的 2 160p、1 080p 的视频测试信号图像。信号源输出的信号已经在海信某车间进行了测试,满足不同型号的电视机主板测试需求。

图 7 NTSC 信号 Fig. 7 NTSC signal

图 8 分量的色差信号 Fig. 8 Component colour signal

图 9 1 080p 的 TMDS 信号 Fig. 9 1 080p TMDS signal

图 10 1 080p 的 TMDS 信号的两场信号 Fig. 10 Two field signals of 1 080p TMDS signal

图 11 信号源彩条及灰度视频信号 Fig. 11 Color bar and gray-scale video signal

# 6 结 论

本视频信号源在一片先进的 Artix-7 系大规模可编程 XC7A100 T 芯片上并行产生多种格式的视频测试信号,如超高清、高清数字视频 HDMI 接口信号和模拟标清视频信号 VGA、CVBS、YPRPB 信号。上位机输出对应视频信号格式及分辨率的控制指令,指令传输给 FPGA 视频信号产生电路部分,在 FPGA 内部产生不同格式和分辨率的标清及超高清、高清数字视频信号,送到不同的视

频接口,输出指令要求的视频测试信号。尤其是在 XC7A100 T芯片内将并行的超高清、高清数字信号转换 成串行差分 TMDS 信号,节省了视频信号的并串转换处 理芯片。整个系统提高了产生视频测试信号的集成度, 方便生产视频设备的厂家进行测试。信号源已经在相关 车间测试,参数满足生产测试要求。

#### 参考文献

- [ 1 ] KANG, Y C, CHANG L W, WU Y C, et al. A 5 Gbps/lane intra-panel interface for ultra-high- definition TFT-LCD application [J]. SID Symposium Digest of Technical Papers, 2015, 46(1): 1278-1280.

- [2] ISHIZONE Y, SUZUKI S, KONISHI K, et al. A 2.0 Gbps intra-panel interface with automatic calibration for chip-on-glass super-high-definition TFT-LCD applications [J]. SID Symposium Digest of Technical Papers, 2014, 45(1): 1191-1194.

- [ 3 ] ZAHIR Y A, HUSSEIN S E, CAI J, et al. Parametric characterization of perceived light field display resolution[J]. SID International Symposium: Digest of Technology Papers, 2016, 47(3): 1241-1245.

- [4] MISELI J. Progess toward the ICDM2 display measurements standard [J]. SID 2017 Digest, 2017, 62(1): 911-914.

- [ 5 ] HATSUMI R, IKEDA H, AOYAMA T, et al. High resolution and low power consumption hybrid display[J]. SID 2017 Digest, 2017, 35(3): 502-504.

- [6] KASTELAN I, PEKOVIC V, TESLIC N, et al. Automatic black box testing of television systems on the final production line [J]. IEEE International Conference on Consumer Electronics, 2011, 57(1): 224-231.

- [7] 朱可, 王磊, 王军,等. 基于 SOPC 的 PC 视频接口自动化检测系统设计[J]. 液晶与显示, 2017,32(9): 714-720.

ZHU K, WANG L, WANG J, et al. Design of PC video interface automatic detection system based on SOPC[J]. Chinese Journal of Liquid Crystals and Displays, 2017, 32(9):714-720.

严中毅, 李凯. 测量仪器与现代微电子、计算机和软

- 件技术的融合[J]. 电子测量与仪器学报, 2015, 29(5):631-637.

YAN ZH Y, LI K. Fusion of measurement equipment and modern microelectronics computer and software technology[J]. Journal of Electronic Measurement and Instrumentation, 2015, 29(5): 631-637.

- [9] 刘敏慧, 孙宝海, 张会新,等. 工业高帧视频编码系统的设计与实现[J]. 仪表技术与传感器, 2018, 1(1):106-108,119.

- LIU M H, SUN B H, ZHANG H X, et al. Design and implementation of industrial high frame video coding system [J]. Instrument Technique and Sensor, 2018, 1(1):106-108,119.

- [10] 张宝龙, 许孝晨, 梅志远, 等. 基于 GMSL 的车载摄像系统研究 [J]. 电子测量与仪器学报, 2021, 35(5): 189-195.

- ZHANG B L, XU X CH, MEI ZH Y, et al. Study on vehicle camera system based on GMSL[J]. Journal of Electronic Measurement and Instrumentation, 2021, 35(5): 189-195.

- [11] 薛倩, 王一虎. 基于 FPGA 的静电层析成像监测系统 研究[J]. 电子测量与仪器学报, 2021, 35(8): 53-61.

- XUE Q, WANG Y H. Research on electrostatic tomography monitoring system based on FPGA [J]. Journal of Electronic Measurement and Instrumentation, 2021, 35(8): 53-61.

- [12] 苗绘玲. 视频时序信号发生器的实现方法[J]. 电视技术, 2016, 40(10):45-49.

MIAO H L. Method of video sequence signal generator[J].

Video Engineering, 2016, 40(10):45-49.

- [13] HYOCHANG K, CHANGSIK Y. A 12-Gb/s HDMI 2.1 quarter-rate transmitter in 28-nm bulk CMOS process[J]. Analog Integrated Circuits and Signal Processing, 2018, 96(1): 363-370.

- [14] KRYJAK T, KOMORKIEWICZ M, GORGON M, et al.

Real-time background generation and foreground object segmentation for high-definition colour video stream in FPGA device [J]. Journal of Real-Time Image Processing, 2012, 9(1); 61-77.

- [15] KOWALCZYK M, CIARACH P, PRZEWLOCKA-RUS D, et al. Real-time FPGA implementation of parallel connected component labelling for a 4K video stream[J]. Journal of Signal Processing Systems, 2021, 93 (1): 481-498.

- [16] 夏正鹏, 李开宇. 高效视频编码(HEVC) 帧内预测的 硬件实现方案 [J]. 电子测量技术, 2017, 40(9): 201-205.

- XIA ZH P, LI K Y. Hardware implementation of high efficiency video coding (HEVC) intra prediction [J]. Electronic Measurement Technology, 2017, 40(9): 201-205.

- [17] 范文斯路,吴乐南. 复合调制 AM 广播接收机的 DL-SAE 码元判决法[J]. 电子测量与仪器学报, 2016, 30(10): 1490-1496.

- FAN W S L, WU L N. Deep learning-sparse autoencoder for symbol discrimination composite AM broadcasting

receiver [J]. Journal of Electronic Measurement and Instrumentation, 2016, 30(10): 1490-1496.

[18] 陈佳楠, 马永涛, 李松, 等. 多目标优化的多存储器内建自测试 [J]. 电子测量与仪器学报, 2020, 34(1): 193-197.

CHEN J N, MA Y T, LI S, et al. Multi-memory built-in self-test based on multi-objective optimization [ J ]. Journal of Electronic Measurement and Instrumentation, 2020, 34(1): 193-197.

- [19] HSIA S C, HSU R C, LIN Y C, et al. Asynchronous control and driver for highspeed LED display with local scanning approach[J]. ET Circuits Devices & Systems, 2019, 14(5): 1-6.

- [20] 贾云辉, 张志宏, 何宏. 基于 ARM-Linux 的爬壁机器 人控制器研究 [J]. 电子测量与仪器学报, 2017, 31(9): 1459-1466.

JIA Y H, ZHANG ZH H, HE H. Research on controller of wall-climbing robot based on ARM-Linux[J]. Journal of Electronic Measurement and Instrumentation, 2017, 31(9): 1459-1466.

[21] 戴学飞, 待鸿彦, 张晓宇. 基于 STM32 降水现象仪检测装置设计 [J]. 电子测量与仪器学报, 2017, 31(10):1596-1601.

DAI X F, DAI H Y, ZHANG X Y. Design of detection device of raindrop spectrometer based on STM32 [ J ]. Journal of Electronic Measurement and Instrumentation, 2017, 31(10): 1596-1601.

#### 作者简介

马家麟, 2018 年于安徽工业大学获得学士学位, 现为青岛大学硕士研究生, 主要研究方向为视频传输技术研究和 FPGA 应用技术研究。

E-mail: ma\_qd\_edu@ 126. com

Ma Jialin received his B. Sc. degree

from Anhui University of Technology in 2018. Now he is a M. Sc. candidate in Qingdao University. His main research

interests include video transmission technology research and FPGA application technology research.

**孙海洲**,2020 年于东北大学获得学士学位,现为青岛大学硕士研究生,主要研究方向为视频传输技术研究和 FPGA 应用技术研究。

E-mail: haizhou\_sun\_97@ 163. com

Sun Haizhou received his B. Sc. degree from Northeastern University in 2020. Now he is a M. Sc. candidate in Qingdao University. His main research interests include video transmission technology research and FPGA application technology research.

任贵珊,2019年于青岛大学获得学士学位,现为青岛大学硕士研究生,主要研究方向为视频传输技术研究和 FPGA 应用技术研究。

E-mail: guishan\_r@ 163. com

Ren Guishan received her B. Sc. degree from Qingdao University in 2019. Now she is a M. Sc. candidate in Qingdao University. Her main research interests include video transmission technology research and FPGA application technology research.

王素珍(通信作者),1988年于东北师范大学获得学士学位,2001年于内蒙古大学获得硕士学位,2010年于山东科技大学获得博士学位,现为青岛大学教授,硕士生导师,主要研究方向为视频传输技术与FPGA应用技术研究。

E-mail: fnwsz111@ 126. com

Wang Suzhen (Corresponding author) received her B. Sc. degree from Northeast Normal University in 1988, M. Sc. degree from the Inner Mongolia University in 2001, and Ph. D. degree from the Shandong University of Science and Technology in 2010. Now she is a professor in Qingdao University. Her main research interests include video transmission and FPGA application technology.